Особенности

• 80C51 Основная Архитектура

• 256 байтов RAM На чипе

• 2048 байтов ERAM На чипе

• Байты 64 КБ Памяти Вспышки На чипе

- Задержание Данных: 10 Лет в 85°C

- Цикл Чтения - записи: 100 КБ

• Кодовая Секция Ботинка с Независимыми Битами Замка

• Байты 2 КБ Вспышки На чипе для Bootloader

• Программирование В системе в соответствии с Программой Ботинка UART На чипе и Способностью IAP

• Байты 2 КБ EEPROM На чипе

Цикл Чтения - записи: 100 КБ

• Интегрированный Монитор Власти (POR: PFD), Чтобы Контролировать Внутреннее Электропитание

• Перерывы с 4 уровнями с 14 источниками

• Три 16-битовых Таймера/прилавка

• Полный Двойной UART Совместимый 80C51

• Быстродействующая Архитектура

- В Стандартном Способе:

40 МГц (Vcc 3V к 5.5V, и Внутреннее и внешнее кодовое выполнение)

60 МГц (Vcc 4.5V к 5.5V и Внутреннее Кодовое выполнение только)

- В способе X2 (6 циклов Часов/машины)

20 МГц (Vcc 3V к 5.5V, и Внутреннее и внешнее кодовое выполнение)

30 МГц (Vcc 4.5V к 5.5V и Внутреннее Кодовое выполнение только)

• Пять Портов: 32 + 4 Цифровых Линии ввода / вывода

• 16-битовый PCA С пятью каналами с

- (8-битовый) PWM

- Быстродействующая Продукция

- Таймер и Захват Края

• Двойной Указатель Данных

• 21-битовый Охранительный Таймер (7 Программируемых Битов)

• 10-битовый Аналог цифрового преобразователя Решения (ADC) с 8 Мультиплексными Входами

• SPI Интерфейс (PLCC52 и пакеты VPFP64 только)

• Логика Эмуляции На чипе (Расширенная Система Крюка)

• Власть, Экономящая Способы

- Праздный Способ

- Способ Власти вниз

• Электропитание: 3 вт к 5.5 вт

• Диапазон температуры: Индустриальный (-40 ° к +85°C)

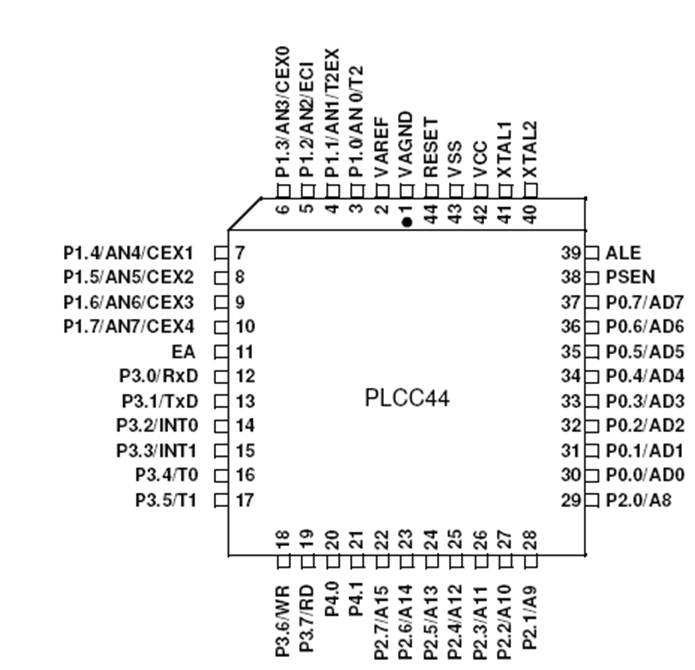

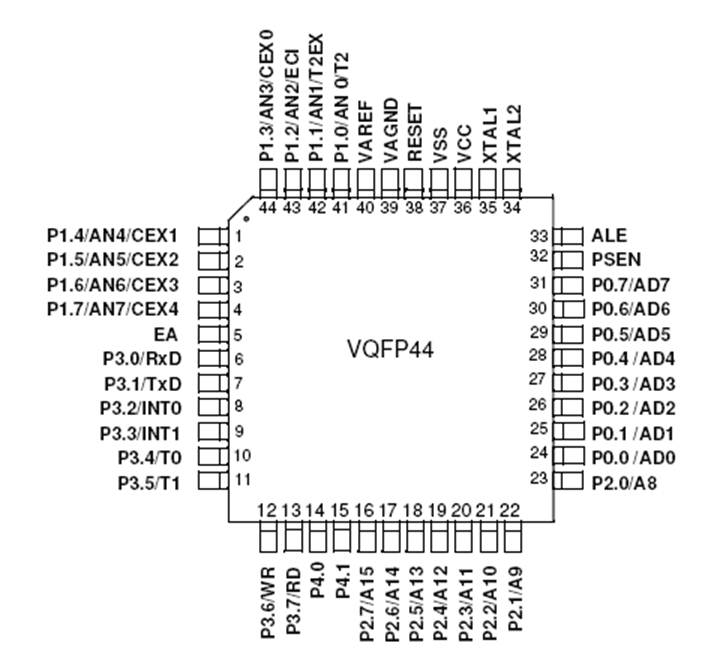

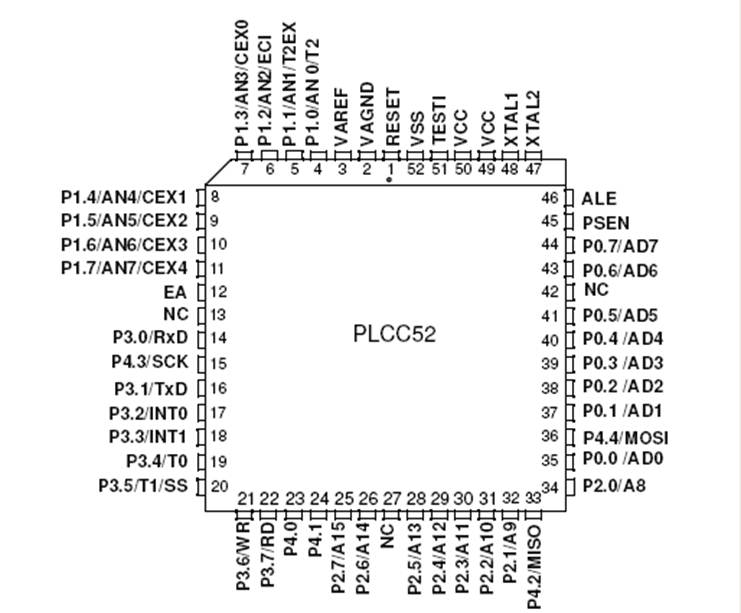

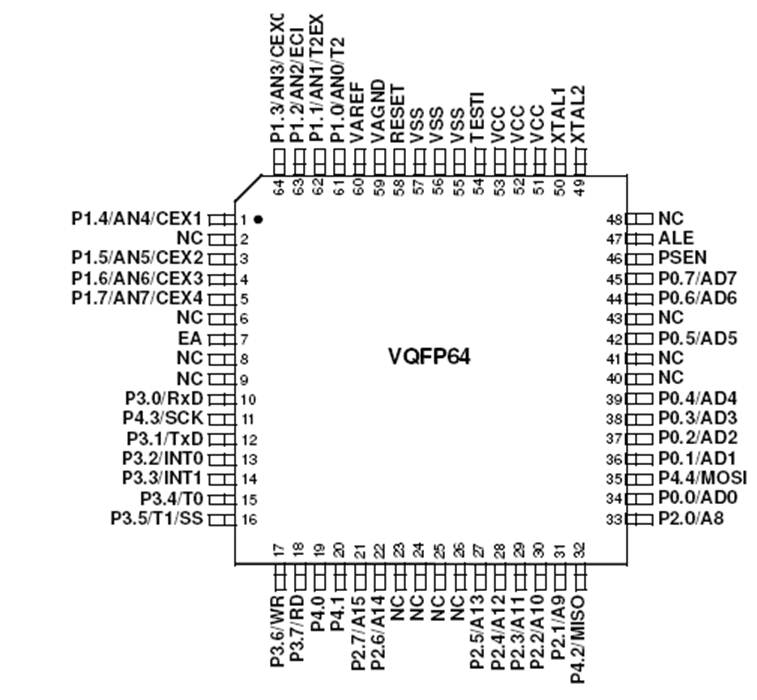

• Пакеты: VQFP44, PLCC44, VQFP64, PLCC52

Описание

AT89C51AC3 - версия Вспышки высокой эффективности 80C51 единственный 8-битовый чип

микродиспетчеры.

В способе X2 максимальная внешняя норма часов 20 МГц достигает 300 не уточнено время цикла.

Помимо AT89C51AC3 обеспечивает Байты 64 КБ памяти Вспышки, включая В системе

Программируя (ISP) и IAP, Память Вспышки Ботинка Байтов 2 КБ, Байты 2 КБ EEPROM и

2048-байтовый ERAM.

Первичное внимание обращено на сокращение электромагнитной эмиссии

AT89C51AC3.

Расширенный 8-битовый

Микродиспетчер

со Вспышкой 64 КБ

Память

AT89C51AC3

2 AT89C51AC3

4383D-8051-02/08

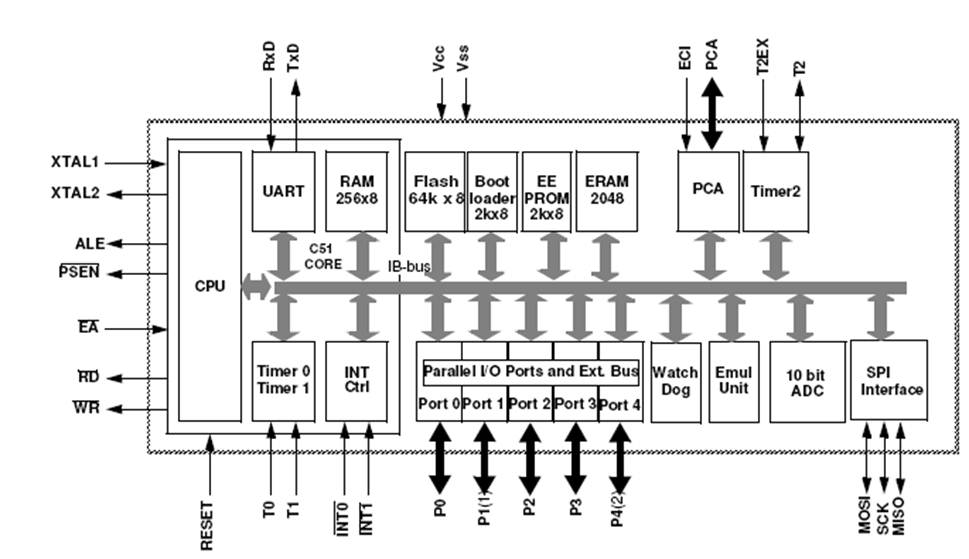

Блок-схема

Примечания: 1. 8 аналоговых Входов/8 Цифровой ввод / вывод

2. 5-битовый Порт ввода / вывода

Описание Типа Названия Булавки

VSS GND основание Кругооборота

TESTI я Должен быть связан с VSS

Напряжение Поставки VCC

Напряжение Ссылки VAREF для ADC

Основание Ссылки VAGND для ADC

Порт ввода / вывода P0.0:7 0:

8-битовая открытая утечка двунаправленный порт ввода / вывода. Порт 0 булавок, которые имеют 1’s написанный им плавание, и в этом государстве, может использоваться как

входы высокого импеданса. Порт 0 является также мультиплексным автобусом адреса и данных младшего разряда во время доступов к внешней Программе

и Память Данных. В этом заявлении это использует сильное внутреннее напряжение-ups, испуская 1’s.

Порт 0 также производит кодовые Байты во время ратификации программы. Внешнее напряжение-ups требуется во время проверки программы.

Порт ввода / вывода P1.0:7 1:

8-битовый двунаправленный порт ввода / вывода с внутренним напряжением-ups. Порт 1 булавка может использоваться для цифрового входа/продукции или как аналоговые входы для

Аналоговый Цифровой Конвертер (ADC). Порт 1 булавка, которые имеют 1’s написанный им, тянут высоко внутренние транзисторы напряжения наверх

и может использоваться как входы в этом государстве. Как входы, Порт 1 булавка, которые тянут низко внешне, будет источником потока

(IIL, см. секцию "Электрическая Особенность") из-за внутреннего напряжения-ups. Порту 1 булавка поручают использоваться как аналог

входы через регистр ADCCF (в этом случае внутреннее напряжение-ups разъединены).

Как вторичная цифровая функция, порт 1 содержит Таймер 2 внешних спусковых механизма и вход часов; внешний вход часов PCA и

ввод / вывод модуля PCA.

P1.0/AN0/T2

Аналоговый входной канал 0,

Внешние часы введены для Timer/counter2.

P1.1/AN1/T2EX

Аналоговый входной канал 1,

Более аккуратный вход для Timer/counter2.

P1.2/AN2/ECI

Аналоговый входной канал 2,

PCA внешние часы введен.

P1.3/AN3/CEX0

Аналоговый входной канал 3,

Модуль PCA 0 Входов input/PWM произведен.

P1.4/AN4/CEX1

Аналоговый входной канал 4,

Модуль PCA 1 Вход input/PWM произведен.

P1.5/AN5/CEX2

Аналоговый входной канал 5,

Модуль PCA 2 Входа input/PWM произведен.

P1.6/AN6/CEX3

Аналоговый входной канал 6,

Модуль PCA 3 Входа input/PWM произведен.

P1.7/AN7/CEX4

Аналоговый входной канал 7,

Модуль PCA 4 Входа ot input/PWM продукция.

Порт 1 получает байт адреса младшего разряда во время программирования стираемой программируемой постоянной памяти и проверки программы.

Это может вести входы CMOS без внешнего напряжения-ups.

Порт ввода / вывода P2.0:7 2:

8-битовый двунаправленный порт ввода / вывода с внутренним напряжением-ups. Порт 2 булавки, которые имеют 1’s написанный им, тянет высоко внутреннее

потяните-ups и может использоваться как входы в этом государстве. Как входы, Порт 2 булавки, которые тянут низко внешне, будут источником

поток (IIL, см. секцию "Электрическая Особенность") из-за внутреннего напряжения-ups. Порт 2 испускает старший байт адреса

во время доступов к внешней Памяти Программы и во время доступов к внешней Памяти Данных, которая использует 16-битовые адреса

(MOVX @DPTR). В этом заявлении это использует сильное внутреннее напряжение-ups, испуская 1’s. Во время доступов к внешним Данным

Память, которые используют адреса на 8 битов (MOVX @Ri), Порт 2, передает содержание специального регистра функции P2.

Это также получает старшие адреса и управляющие сигналы во время ратификации программы.

Это может вести входы CMOS без внешнего напряжения-ups.

6 AT89C51AC3

4383D-8051-02/08

Порт ввода / вывода P3.0:7 3:

8-битовый двунаправленный порт ввода / вывода с внутренним напряжением-ups. Порт 3 булавки, которые имеют 1’s написанный им, тянет высоко внутреннее

транзисторы напряжения наверх и могут использоваться как входы в этом государстве. Как входы, Порт 3 булавки, которые тянут низко внешне, будут a

источник потока (IIL, см. секцию "Электрическая Особенность") из-за внутреннего напряжения-ups.

Замок продукции, соответствующий вторичной функции, должен быть запрограммирован к одному для той функции, чтобы работать (за исключением

TxD и WR). Вторичные функции назначены на булавки порта 3 следующим образом:

P3.0/RxD:

(Асинхронный) ввод данных приемника или ввод данных / производят (синхронный) из последовательного интерфейса

P3.1/TxD:

Данные передатчика производят (асинхронный), или часы производили (синхронный) из последовательного интерфейса

P3.2/INT0:

Внешний перерыв 0 входов/таймеров 0 контрольно-пропускной службы введен

P3.3/INT1:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.