Федеральное агентство связи

Государственное образовательное учреждение высшего профессионального образования

«Сибирский государственный университет телекоммуникаций и информатики»

(ГОУ ВПО «СибГУТИ»)

Кафедра ТС и ВС

по дисциплине

“ЦОС и сигнальные процессоры”

на тему

Демодулятор сигналов ОФМ с вращением фазы

Выполнил:

студентгруппы С-48

C.

Проверил:

Оглавление

1. Задание на курсовое проектирование. 3

2. Введение. 4

3. Общая структурная схема приемника. 5

4. Описание работы разрабатываемого устройства. 6

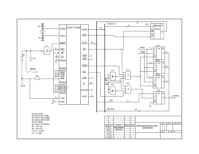

5. Функциональная схема демодулятора. 7

6. Обобщенный алгоритм работы демодулятора. 8

7. Детализированный алгоритм работы демодулятора. 9

8. Расчет параметров таймера для формирования частоты дискретизации. 10

9. Алгоритм основной программы MAIN.. 11

10. Диаграмма распределения регистров и ячеек памяти. 12

11. Схема алгоритма на языке ассемблера ЦСП.. 13

12. Доработка с целью использования многофункциональных инструкций. 14

13. Подпрограмма на языке ассемблера (файл DEM.DSP) 14

14. Программа на языке ассемблера ЦСП (файл MAIN.DSP) 14

15. Файл описания системы SYST.SYS. 15

16. Карты использования памяти. 16

17. Функциональная схема. 17

18. Испытание на имитаторе. 19

19. Заключение. 20

20. Библиография. 21

СибГУТИ

Кафедра ТС и ВС

ЗАДАНИЕ 10

на курсовую работу

по дисциплине “ЦОС и сигнальные процессоры”

студенту группы С –48 Шулятицкому И.С.

Разработать устройство на цифровом сигнальном процессоре ADSP-2189 по следующим техническим условиям:

1. Наименование устройства: приемник

2. Разрабатываемый узел устройства: Демодулятор сигналов ОФМ с вращением фазы

3. Исходные сведения и литература: Л 11, Л 12, Л/р 8

4. Источник синхросигналов: внутренняя 11 МГц

5. Порт ввода: 10 – разрядный

6. Порт вывода: 1 – разрядный

7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

СОДЕРЖАНИЕ ПРОЕКТА

Разработка программы на языке ассемблера ADSP-21xx.

Разработка функциональной схемы устройства на ADSP-2189М.

Оценка затрат времени на выполнение программы.

Чертежи: Детальная схема алгоритма.

Функциональная схема устройства.

Дата выдачи задания 10.03.07. Срок сдачи проекта 10.05.07.

Руководитель/ Е. Н./

Главная цель курсового проектирования состоит в том, чтобы через активный процесс разработки аппаратных и программных средств, приобрести углубленное понимание принципов, лежащих в основе работы ЭВМ и их использование в технике связи.

Многочисленные семейства цифровых сигнальных процессоров внедряются в тех областях техники, где первоначально доминировали схемы аналоговой обработки сигнала. Спектр применения DSP очень широк и охватывает диапазон от простых традиционных модемов до радио- и гидролокационных систем, в которых требуется сверхвысокое быстродействие.

ADSP-2189М представляет собой оптимизированный для цифровой обработки сигналов (DSP) и других применений, требующих высокоскоростных вычислительных операций. ADSP-2189М изготовлен по высокоскоростной 1.0-микронной КМОП технологии с двухслойной металлизацией. Любая инструкция выполняется за один цикл. Изготовление по моп-технологии обеспечивает низкое потребление энергии.

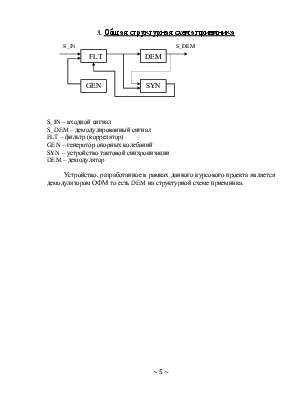

S_IN S_DEM

|

S_IN – входной сигнал

S_DEM – демодулированный сигнал

FLT – фильтр (коррелятор)

GEN – генератор опорных колебаний

SYN – устройство тактовой синхронизации

DEM – демодулятор

Устройство, разработанное в рамках данного курсового проекта является демодулятором ОФМ то есть DEM на структурной схеме приемника.

Устройство предназначено для демодуляции синхронных сигналов с относительной фазовой модуляцией (ОФМ). Оно содержат генератор двух опорных колебаний, находящихся в квадратуре, два коррелятора, два блока стробирования, решающий блок и блок тактовой синхронизации.

Коррелятор состоит из последовательно соединенных перемножителя и интегратора. В интеграторе производится накопление на интервале Т элемента сигнала результатов перемножения принимаемого сигнала и опорного колебания с целью улучшения отношения сигнал/помеха. В конце этого интервала блок стробирования обеспечивает взятие отсчета корреляционной функции для последующей обработки, после чего интегратор сбрасывается в нуль и начинается такая же обработка следующего элемента сигнала. Управляющие импульсы, необходимые для правильной работы блоков стробирования и сброса интеграторов, обеспечивает блок тактовой синхронизации, обязательно присутствующий в корреляционном приемнике. Благодаря блоку тактовой синхронизации демодулятор использует сведения об ожидаемом положении во времени границ элементов сигнала, что обеспечивает более высокую помехоустойчивость приемника. Ослабление влияния помех на блок тактовой синхронизации ведет к получению более точных сведений о границах элементов сигнала, что, в конечном итоге, ведет к повышению помехоустойчивости приемника в целом. Отсчеты корреляционных функций с выходов блоков стробирования поступают в решающий блок, где вычисляются оценки правдоподобия и на основании сравнения их значений выдается решение о переданном состоянии сигнала.

Приемник работает следующим образом: входной сигнал приемника подводится к корреляторам , выполняющим роль оптимального фильтра, ослабляющего действие помех. В корреляторах происходит умножение сигнала на находящиеся в квадратуре выходные колебания опорного генератора, интегрирование результатов перемножения на протяжении тактового интервала и сброс результатов интегрирования в нуль в конце каждого тактового интервала управляющими импульсами. В блоках стробирования с помощью управляющих импульсов берутся отсчеты выходных сигналов корреляторов в моменты, предшествующие их сбросу. Получаемые отсчеты корреляционных функций X и Y пропорциональны уровню сигнала на входе приемника и находятся в квадратуре. В решающем блоке по отсчетам корреляционных функций вычисляются оценки правдоподобия для ожидаемых состояний сигнала и на основе их сравнения принимается решение о приеме того из состояний сигнала, для которого получена большая оценка. При однократной ОФМ переход фазы на 180 вызывает появление "1" на выходе приемника, а отсутствие перехода фазы - "0".

S_filt

S_dem

БВКП БПР

t 90

t - задержка сигнала

БПР – блок принятия решения

БВФП - блок вычисления функционала правдоподобия Z

90 - блок вращения фазы на 90 градусов

S_Flt – сигнал с фильтров

S_Dem – демодулированный сигнал

Демодулятор работает следующим образом: сигнал с фильтра и сигнал предыдущей посылки ,сдвинутый по фазе на 90 градусов ,поступают в БВПР, где вычисляется функционал Z.

Если результат перемножения Z оказался больше нуля

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.