Федеральное агентство по образованию

Государственное образовательное учреждение

Высшего профессионального образования

Рязанский государственный радиотехнический университет

Кафедра АИТУ

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовому проекту по курсу:

«Программирование цифровых устройств на ПЛИС»

на тему:

«Устройство для преобразования кода»

Выполнил: студент гр. 730

Проверил:

Рязань, 2011

Содержание

1. Задание 3

2. Структурная схема проекта и ее описание 4

3. Структурная схема декодера и описание метода его построения 6

4. Алгоритм работы CRC-декодера 8

5. Схемы подпроектов и результаты их моделирования 8

Декодер 8

Формирователь пускового импульса 11

Делитель частоты 13

Устройство управления 14

Сдвиговый регистр 15

Дешифратордля управления 7-сегментным индикатором 17

6. Схема проекта, описание работы и временные диаграммы, полученные в результате моделирования 18

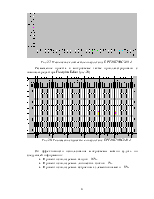

7. Размещение проекта на кристалле 21

8. Назначение контактов микросхемы EPF10K70RC240-4 для портов проекта 21

9. Описание процедуры ввода проекта в микросхему

EPF10K70RC240-4 на учебной плате UP2 Educational Kit 24

10. Определение временных задержек и быстродействия устройства 24

11. Заключение 27

12.Библиографический список 28

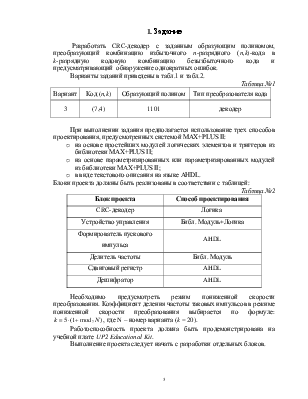

1. Задание

Разработать CRC‑декодер с заданным образующим полиномом, преобразующий комбинацию избыточного n-разрядного (n,k)‑кода в k‑разрядную кодовую комбинацию безызбыточного кода и предусматривающий обнаружение однократных ошибок.

Варианты заданий приведены в табл.1 и табл.2.

Таблица №1

|

Вариант |

Код (n,k) |

Образующий полином |

Тип преобразователя кода |

|

3 |

(7,4) |

1101 |

декодер |

При выполнении задания предполагается использование трех способов проектирования, предусмотренных системой MAX+PLUS II:

o на основе простейших модулей логических элементов и триггеров из библиотеки MAX+PLUS II;

o на основе параметризированных или параметризированных модулей из библиотеки MAX+PLUS II;

o в виде текстового описания на языке AHDL.

Блоки проекта должны быть реализованы в соответствии с таблицей:

Таблица №2

|

Блок проекта |

Способ проектирования |

|

CRC-декодер |

Логика |

|

Устройство управления |

Библ. Модуль+Логика |

|

Формирователь пускового импульса |

AHDL |

|

Делитель частоты |

Библ. Модуль |

|

Сдвиговый регистр |

AHDL |

|

Дешифратор |

AHDL |

Необходимо предусмотреть режим пониженной

скорости преобразования. Коэффициент деления частоты таковых импульсов в режиме

пониженной скорости преобразования выбирается по формуле: ![]() , где N – номер варианта (k =

20).

, где N – номер варианта (k =

20).

Работоспособность проекта должна быть продемонстрирована на учебной плате UP2 Educational Kit.

Выполнение проекта следует начать с разработки отдельных блоков.

2. Структурная схема проекта и ее описание

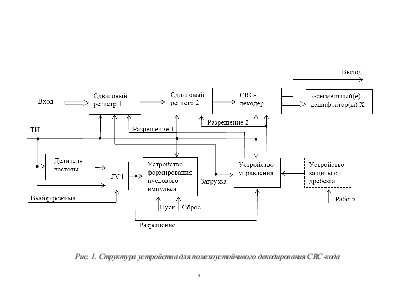

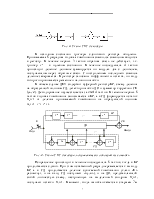

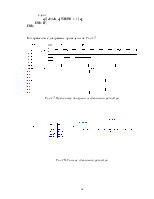

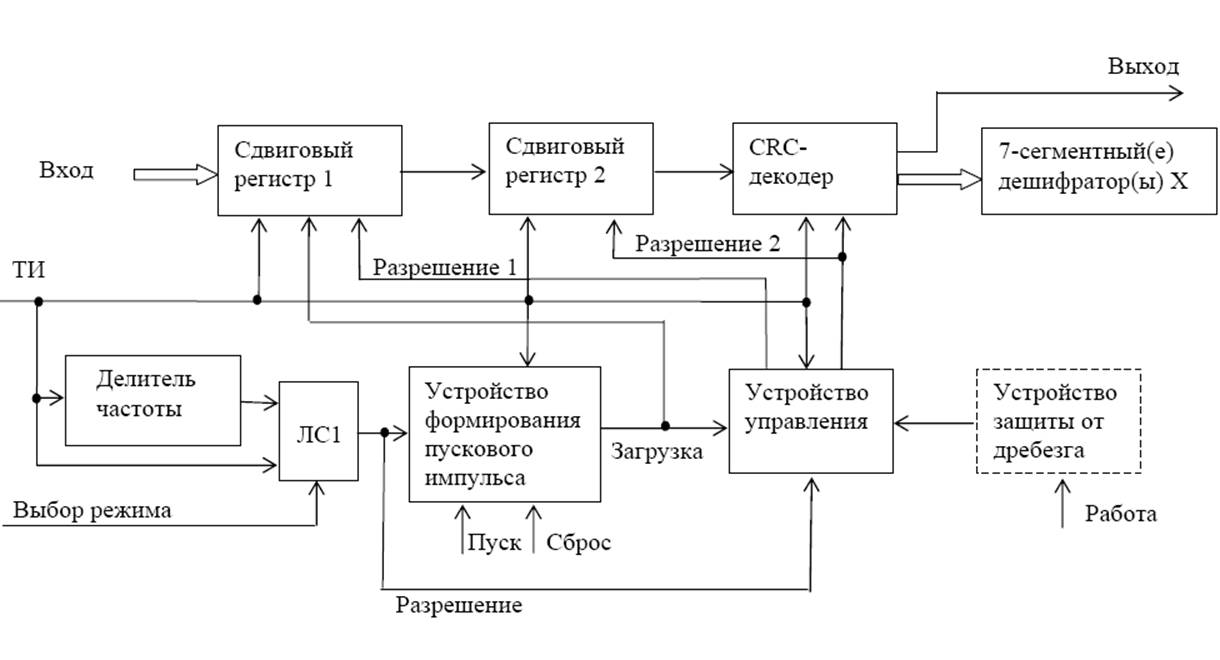

Устройство для помехоустойчивого декодирования реализовано по схеме на рис.1.

Согласно этой схеме первые 4 разряда декодируемой комбинации вводится параллельным кодом в сдвиговый регистр 1 и затем сдвигаются в регистр 2. Затем вводятся очередные 4 разряда. После того как вся кодовая комбинация оказывается записанной в регистрах 1 и 2 производится ее поразрядный вывод на CRC-декодер. Полученный в декодере остаток от деления на образующий полином поступает на дешифратор для отображения на 7-сегментном индикаторе платы UP2 Educational Kit.

Работа устройства протекает под управлением тактовых импульсов ТИ. Предусматривается два режима работы устройства:

· с частотой следования тактовых импульсов ТИ, когда простейшие операции в устройстве происходят через интервалы, равные периоды следования ТИ;

· с пониженной в 20 раз частотой, когда простейшие операции в схеме происходят в моменты действия каждого 30-ого ТИ.

Режим работы устанавливается логической схемой ЛС1 по сигналам с выхода делителя частоты и управляющему сигналу «Выбор режима» принимающему значение логического нуля и единицы.

При работе с частотой следования ТИ на выходе логической схемы ЛС1 формируется сигнал «Разрешение» постоянного уровня, разрешающий работу всех блоков устройства. При работе с пониженной в 30 раз частотой ТИ на выходе логической схемы ЛС1 формируется импульсный сигнал, разрешающий работу устройства только в моменты действия каждого 30-ого ТИ.

Рис. 1. Структура устройства для помехоустойчивого декодирования CRC-кода

«Устройство выбора частоты» формирует сигнал «Общее разрешение» для обеспечения работы в выбранном режиме.

Работа устройства должна начинаться по сигналу «Пуск» (логический ноль), который формируется при нажатии нефиксируемой кнопки на плате UP2 Educational Kit. Для синхронизации сигнала «Пуск» с тактовыми импульсами ТИ применяется устройство формирования пускового импульса, привязывающее момент пуска к очередному тактовому импульсу. Сигнал «Сброс» необходим для восстановления устройства формирования пускового импульса в исходное состояние, а также приведения всех устройств в исходное состояние.

По сигналу «Пуск» на выходе устройства формирования пускового импульса появляется сигнал «Загрузка», записывающий кодируемую безызбыточную комбинацию или ее часть в сдвиговый регистр 1, а при одновременном единичном сигнале «Работа» запускает устройство управления работой декодера, которое формирует сигнал управления «Разрешение 1» и «Разрешение 2». По сигналу «Разрешение 1» происходят запись и сдвиги в регистре 1. По сигналу «Разрешение 2» происходят сдвиги в сдвиговом регистре 2 и CRC-декодере для вывода полученной комбинации на индикатор.[1]

3. Структурная схема декодера и описание метода его построения

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.