Новый REX - префикс вводится для определения 64-разрядного размера операнда и новых регистров.

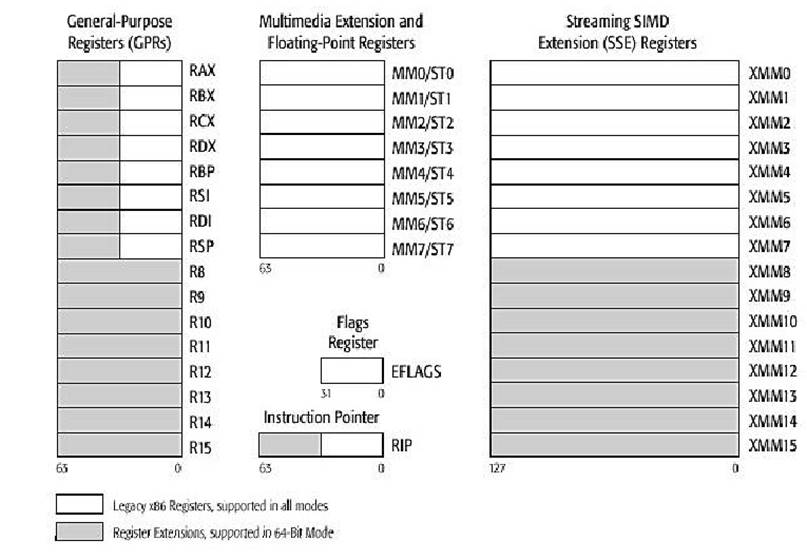

Режим допускается операционной системой на индивидуальном базисе сегмента кода. Новые расширения регистра, добавленные через новый префикс прибавляет восемь 64-разрядных РОНов (R8-R15), восемь 128-разрядных потоковых (цепочек) SIMD регистров (XMM8-XMM15), и расширяет все РОНы и указатель команды на 64 бита. REX префикс дает новую возможность регистра- байта которая делает младший байт любого РОНа, возможным для байтовых операций.

Это приводит к однородному набору байта, слово, двойные слова (dword), и квадрослова (qword) использовать лучше для распределения регистров компилятора. Указатель команды также расширен к 64 битам.

АМDx.86

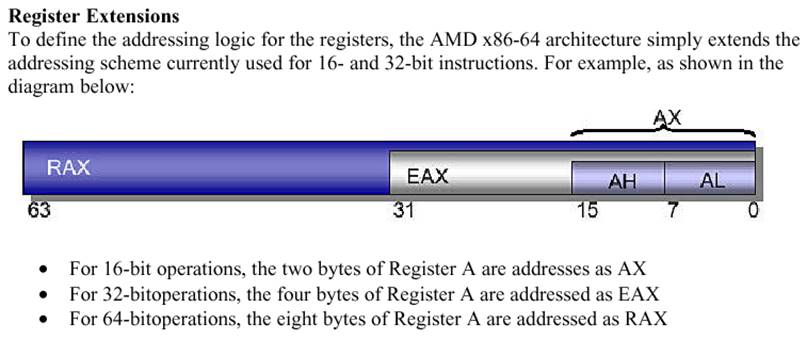

Удлинение регистров.

Чтобы определять логику адресования для регистров, архитектура AMD x86-64 расширяет методы адресации, в настоящее время использованные для 16- и 32-разрядных команд.

Например, как показано в диаграмме ниже:

·Для 16-разрядных операций, два байта Регистра А – адресуются как АХ

Для 32-bit операций, четыре байта Регистра А адресуются как EAX

Для 64-bit операндов, восемь байтов Регистра А адресованы как RAX.

В 64-разрядном режиме, РОНы расширены до 64-bits.

64-разрядные регистраторы названы RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP, RIP и RFLAGS. Новые 64-разрядные регистры покрывают и расширяют существующие регистры.

Кроме того, восемь новых 64-разрядных РОНов добавлены к 16 GPRS. новые РОНы названы R8 –R15. Расширения регистров также прибавляют восемь новых потоковых регистров SIMD к 16 SIMD регистрам.

Новые регистры SIMD названы XMM8 - XMM15.

Регистры сегмента (ES, DS, FS, GS и SS) игнорируются в 64-разрядном режиме.

Кодовый сегмент -CS существует в 64-разрядном режиме и необходим для того чтобы формировать заданный по умолчанию режим процессора (16 -, 32- или 64-разрядный режим) а также в привилегированном режиме выполнения.

Как отмечено выше, D бит и L бит используется, чтобы определить заданный по умолчанию адрес и размеры операнда. DPL используется для проверок привилегии выполнения. Поля базы и предела игнорируются.

При выполнении 32-разрядных операций и регистра адресата - РОНы ,

32-разрядное значение будет расширенное нулем в полный 64-разрядный РОН.

8-разрядные и 16-разрядные операции на РОНах сохраняют все незаписанные верхние биты. Что сохраняет 16- и 32-разрядных семантики для различных результатов.

В коечном результате это просто позволяет набор префиксов команды, которые определяют, что 64-разрядный операнд имеет доступ к новым регистрам.

Это подобно методу, который ранее использовался для расширения x86 архитектуры для других функциональных возможностей, типа AMD'S 3DNow! ™ технология.

С этой стратегией, AMD делает это возможным для поставщиков платформы, разработчиков, и других пользователей, чтобы использовать существующий. комплекты инструментальных средств, приложения, и знание, при обеспечении плавного перемещения к 64-разрядным приложениям для аппаратных и программных разработок.

Режим совместимости.

Режим совместимости позволяет операционным системам, осуществлять двоичную совместимость с существующими 16-разрядными и 32-разрядными x86 приложениями. Это позволяет этим приложениям, работать, без перетрансляции, под 64-разрядной операционной системой в длинном режиме.

В режиме совместимости, приложения могут обращаться только к первым 4GBytes виртуального адресного пространства. В стандарте x86 префиксы команды переключаются между 16-разрядным и 32-разрядным адресом и размерами операнда. Как с 64-разрядным режимом, режим совместимости допускается операционной системой на базисе индивидуального сегмента кода.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.