Таблица №1.5 Таблица состояний счетчика на 4.

|

№ |

Текущие |

Последующие |

J1 |

K1 |

J2 |

K2 |

||

|

Q1 |

Q2 |

Q1 |

Q2 |

|||||

|

0 |

0 |

0 |

0 |

1 |

0 |

~ |

1 |

~ |

|

1 |

0 |

1 |

0 |

1 |

1 |

~ |

~ |

1 |

|

2 |

0 |

1 |

0 |

1 |

~ |

0 |

1 |

~ |

|

3 |

0 |

1 |

0 |

1 |

~ |

1 |

~ |

1 |

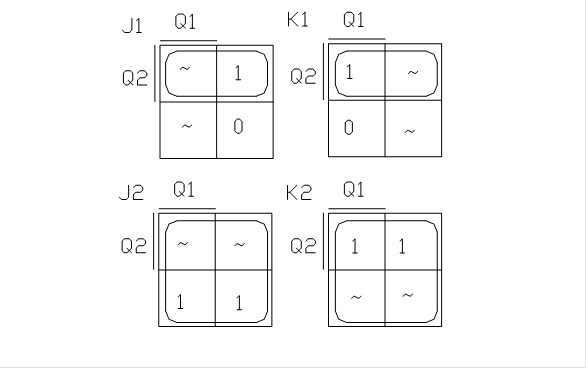

По таблице истинности составим функции для входов триггеров. И минимизируем их с помощью карт Карно (рисунок№1.7).

Рисунок№1.7

Получаем минимальные функции для:

![]()

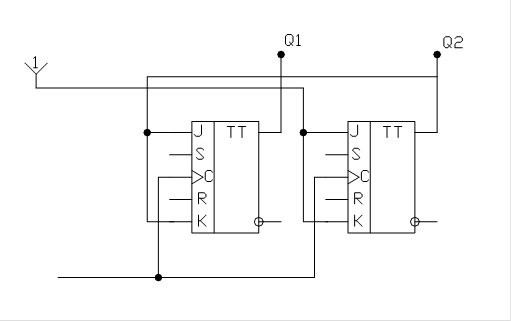

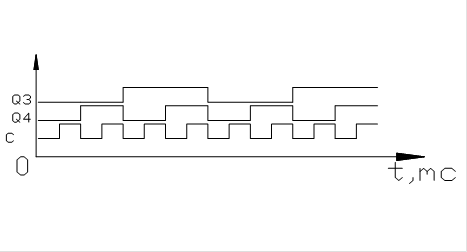

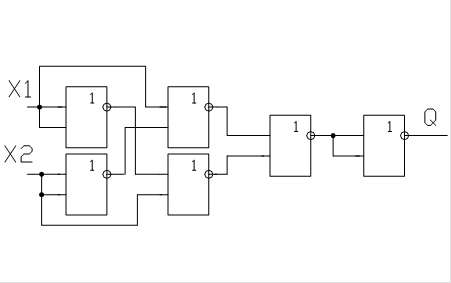

Схема счетчика представлена на рисунке№1.8 , а диаграмма работы на рисунке№1.9.

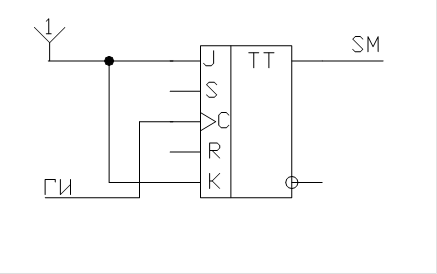

Рисунок№1.8

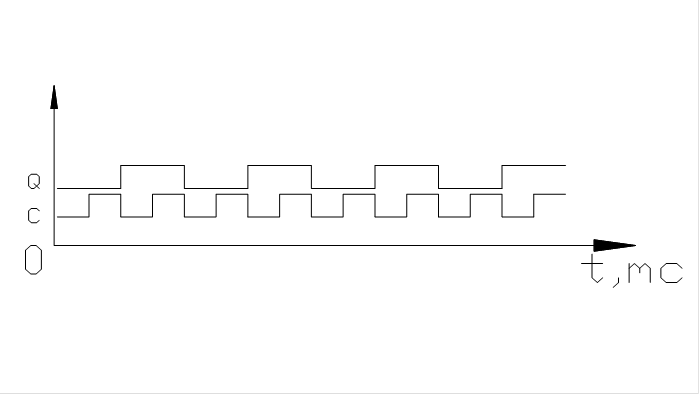

Рисунок№1.9

Рисунок№1.10

1.5 Разработка делителя частоты.

Делитель частоты – устройство, на вход которого подаются импульсы с частотой f ,а на выходе формируются с частотой f’ = f / k. Где k - коэффициент деления.

Соберём делитель частоты на 2 на одном JK-триггере (рисунок 1.11). Для этого необходимо соединить входы J и K и подать на них логическую единицу. На вход синхронизации будут поступать импульсы с генератора импульсов, тогда на выходе мы получим частоту уменьшенную вдвое чем на генераторе импульсов. На рисунке№1.12 показана временная диаграмма работы делителя частоты.

Рисунок№1.11

1.6 Разработка сумматора по модулю два.

Сумматор – устройство, считающее количество активных сигналов на входе.

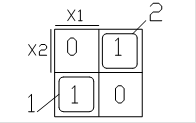

В данном варианте требуется создать сумматор по модулю два всего на два входа. Один вход будет подведён с мультиплексора, другой с делителя частоты. Для сумматора составим таблицу истинности (таблица№1.6).

Таблица 1.6 Таблица состояний сумматора.

|

Входы |

Выход |

|

|

x1 |

x2 |

Q |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

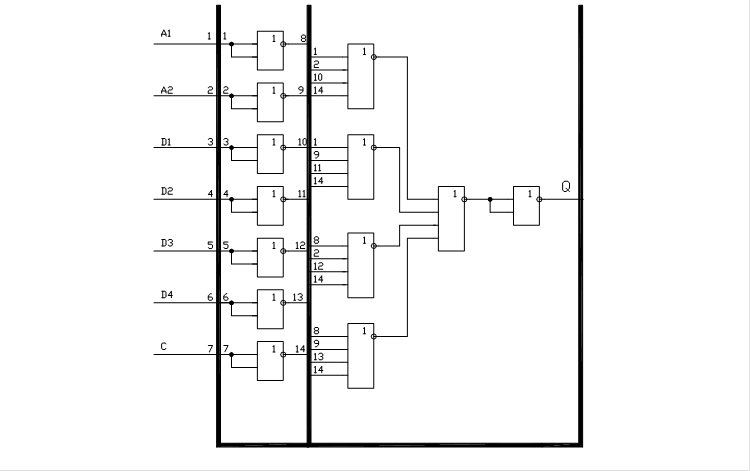

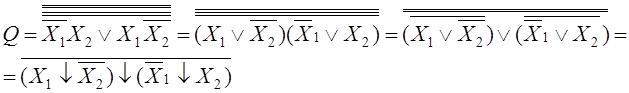

По таблице истинности составим функцию для выхода Q.

![]()

Для построения схемы (рисунок 1.13) перейдём к базису ИЛИ-НЕ:

Рисунок№1.13

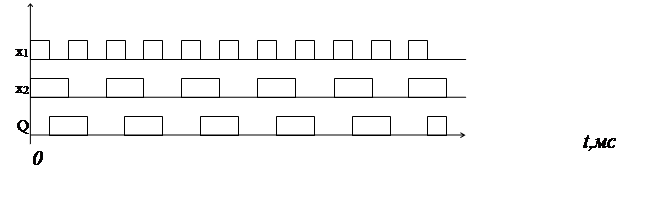

Наглядная демонстрация представлена на рисунке№1.14

|

Рисунок№1.14

1.7 Выбор элементной базы дискретного устройства.

2. Синтез абстрактного конечного автомата

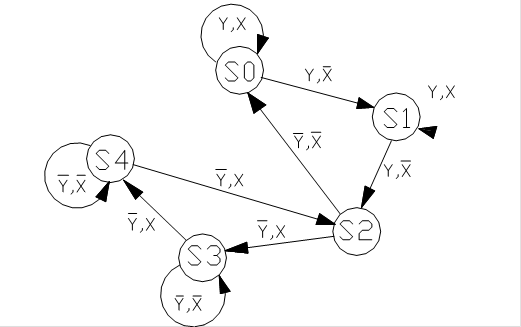

Требуется синтезировать синхронный автомат, заданный таблицей переходов(таблица№2.1) и таблицей выходов(таблица№2.2). В качестве элементов памяти используется JK-триггеры, базис реализации ИЛИ-НЕ.

Автоматом называется дискретное устройство, способное принимать различные состояния, под воздействием входных сигналов, переходить из одного состояния в другое и вырабатывать выходные сигналы.

Синхронные автоматы представляют собой подкласс автоматов, в которых исключение критических состязаний достигается за счёт синхронизации появления внешних и внутренних сигналов в схеме.

Таблица№2.1 Таблица переходов.

|

|

a1 |

a2 |

|

S |

||

|

S0 |

S1 |

<S0> |

|

S1 |

S2 |

<S1> |

|

S2 |

S0 |

S3 |

|

S3 |

<S3> |

S4 |

|

S4 |

<S4> |

S2 |

Таблица№2.2 Таблица выходов.

|

|

a1 |

a2 |

|

S |

||

|

S0 |

1 |

1 |

|

S1 |

1 |

1 |

|

S2 |

0 |

0 |

|

S3 |

0 |

0 |

|

S4 |

0 |

0 |

Графический метод основывается на представлении автомата в форме графа. В качестве элементов памяти могут использоваться различные типы триггеров, в данном варианте элементами памяти являются JK-триггеры.

Таблицам №2.1 и №2.2 соответствует граф, представленный на рисунке №2.1.

Рисунок№2.1

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.