Минимизируем функции счетчика методом карт Карно.

Q2

|

Q1 0

0 1 1

Q1 0

0 1 1

* * 1 1

![]()

0 0 0 0 Q3 J2=Q1Q2

0 0 0 0

Q4

Q2

|

1 1 0 0

1 1 0 0

Q1

* * 0 0 J3=Q1Q2

Q3

0 0 0 0

0 0 0 0

Q4

Q2

|

Q1 0 0 0 0

|

* * 0 0

![]()

![]() Q3

J4=Q2Q3

v Q1Q3

Q3

J4=Q2Q3

v Q1Q3

1 1 1 1

0 0 0 0

Q4

Рис 1.4. Упрощение ФАЛ методом карт Карно

Схема счетчика приведена на принципиальной схеме дискретного устройства.

1.3 Делитель частоты

В задании курсового проекта не был задан коэффициент деления, и поэтому синтезируем делитель с коэффициентом деления – 128.

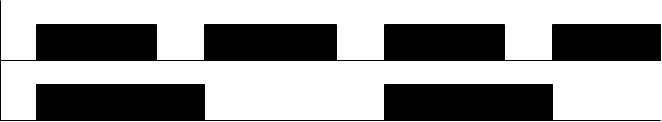

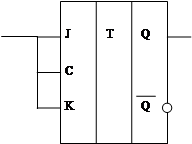

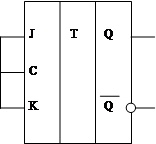

Делитель строится на D-триггерах. D-триггер – есть JK-триггер с объединенными J и K входами [л2.218]. Ввиду большого размера временной диаграммы делителя приведем диаграмму работы делителя частоты на 2. На диаграмме делителя на 128 на каждый выходной импульс придется 128 входных.

|

Рис 1.5. Временная диаграмма делителя частоты

|

|

|

![]()

![]()

![]()

![]() …

…

DD1 DD6 DD7

Рис 1.6. Схема делителя частоты

1.4 Мультиплексор

Мультиплексор – устройство передающее сигналы на выход в последовательности зависящей от сигналов на адресных входах и входах данных [л1.143]. В нашем случае входами данных Х1 Х2 Х3 Х4 будут являться выходы счетчика Q1 Q2 Q3 Q4. На адресные входы необходимо подать следующие кодовые комбинации:

Таблица 1.2. Состояние адресных входов мультиплексора

|

A1 |

A2 |

|

0 |

0 |

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

Следовательно можно подать на адресные входы импульсы с выходов счетчика Q1 и Q2. Мультиплексор работает по схеме совпадения. На выходе мультиплексора тогда будет еденица, когда появится еденица на одном из входов данных и соответствующем коде адресных входов. Работу мультиплексора можно показать на временной диаграмме.

![]() А1

А1

![]()

![]()

![]()

![]()

![]()

![]() А2

А2

![]() Q1

Q1

![]()

![]()

![]() Q2

Q2

![]() Q3

Q3

![]()

![]()

![]() Q4

Q4

![]() Y

Y

Рис 1.7. Временная диаграмма работы мультиплексора

Схема мультиплексора приведена в принципиальной схеме дискретного устройства.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.