Таблица 2.4 Таблица переходов.

|

|

a1 |

a2 |

|

000 |

100 |

000 |

|

001 |

001 |

010 |

|

010 |

010 |

011 |

|

011 |

011 |

001 |

|

100 |

000 |

100 |

Таблица 2.5 Таблица выходов.

|

|

a1 |

a2 |

|

000 |

0 |

1 |

|

001 |

0 |

1 |

|

010 |

1 |

0 |

|

011 |

0 |

1 |

|

100 |

0 |

0 |

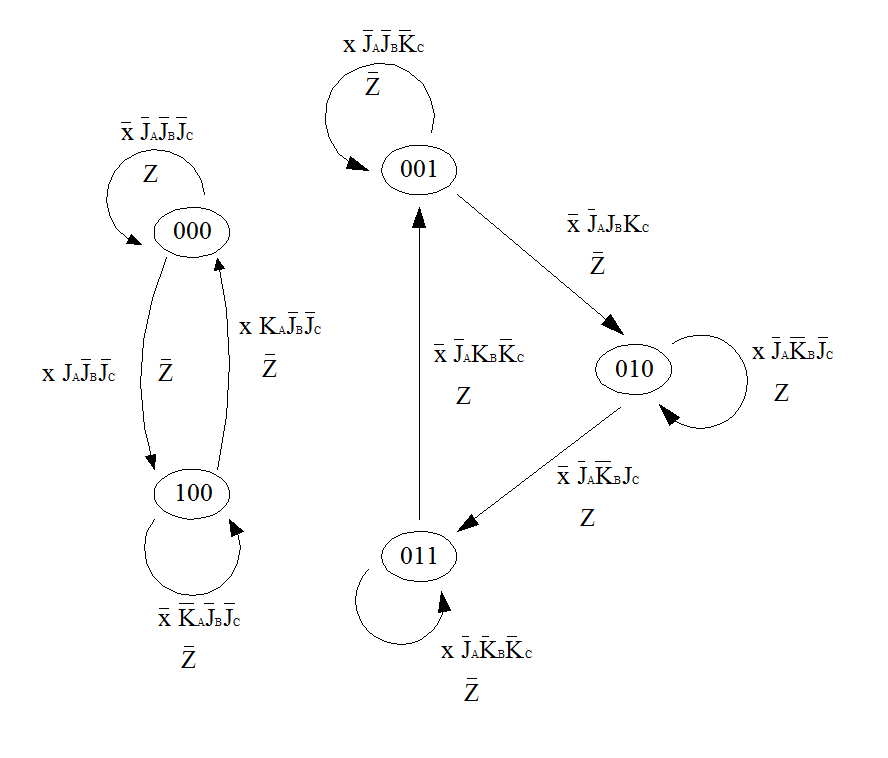

На основании таблицы переходов и таблицы выходов составим граф (рис. 2.1), на вершинах которого обозначены внутренние состояния, а на ветвях: JA , KA , JB , KB , JC , KC - состояния входов триггеров для заданного перехода ; x - значение на входе: a1 - “0”, a2 - “1” ; z - значение на выходе синхронного автомата.

Таблица 2.6 Таблица переходов JK-Триггера.

|

Переход |

J |

K |

|

|

0 |

0 |

0 |

- |

|

0 |

1 |

1 |

- |

|

1 |

0 |

- |

1 |

|

1 |

1 |

- |

0 |

![]()

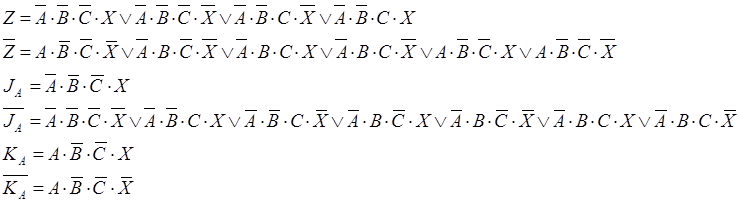

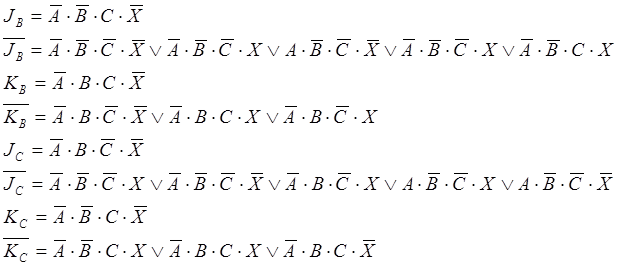

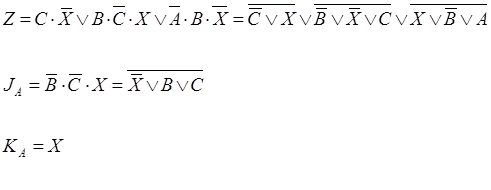

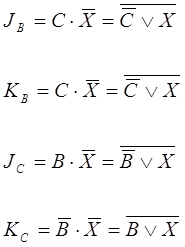

На основании данного графа можно записать функции возбуждения и выходов автомата:

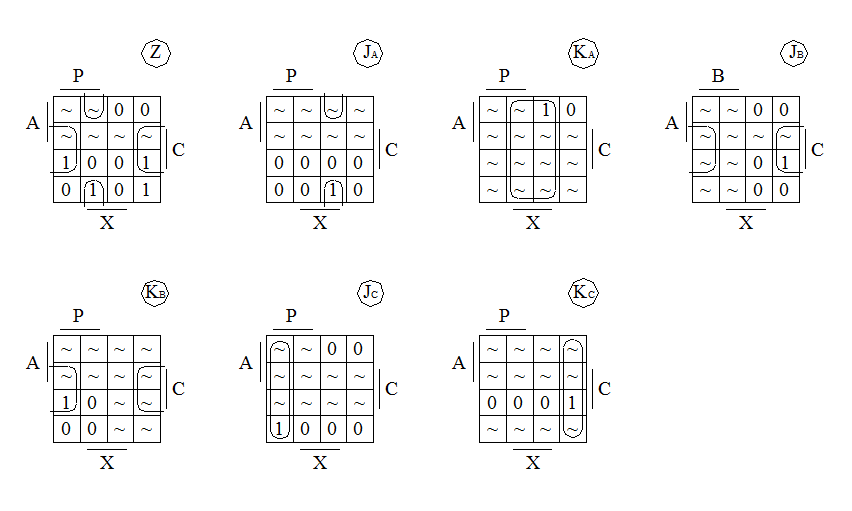

Полученные функции минимизируем с помощью карт

Карно:

По полученным функциям строим синхронный автомат.

Схема электрическая принципиальная автомата приводится в приложении.

Автомат состоит из следующих структурных частей: схемы синхронизации (СС), реализованной на логических элементах DD1 и триггерах DD2 – DD3, логического преобразователя (ЛП), реализованного на логических элементах DD4 – DD7, DD8.1 – DD8.3, элементов памяти (ЭП) (триггеры DD9 – DD10) и выходного преобразователя (ВП) (логический элемент DD8.4). СС предназначена длясинхронизации работы отдельных элементов автомата, что обеспечивается подачей тактовых импульсов на входы С1 и С2 автомата, кроме того наличие СС позволяет исключать критические состязания аппаратным методом .

Логический преобразователь ЛП необходим для определения состояния элементов памяти на триггерах и реализуется в соответствии с таблицей переходов .

Выходной преобразователь позволяет получить выходную функцию, заданную таблицей выходов .

В курсовом проекте было разработано дискретное устройство и синтезирован абстрактный конечный автомат. Так же получены навыки разработки цифровых устройств, таких как генератор, счётчик, делитель частоты, преобразователь кода, сумматор. Изучена методика минимизации функций алгебры-логики несколькими методами. Были освоены принципы построения надёжных схем и способы исключения критических состязаний. Изучены обозначения ГОСТ для электрических принципиальных схем.

1. Сапожников В.В., Кварцов Ю.А, Сапожников Вл.В. “Дискретные устройства железнодорожной автоматики телемеханики и связи”: М., “Транспорт ”, 1988.

2. Пухальский Г.И., Новосельцева Т.Я. “Проектирование дискретных устройств на интегральных микросхемах”: М., “Радио и связь ”, 1990.

3. Бочков К.А., Кострома Т.В., Семенюта А.Н.. “Синтез дискретных устройств. Методические указания для выполнения курсового проекта по курсу “Теоретические основы автоматики и телемеханики”: Гомель, 1991.

4. Шило В.Л. “Популярные цифровые микросхемы”: Справочник, Челябинск, “Металлургия”, 1994.

5. Богданович М.И и др. “Цифровые интегральные микросхемы”: Справочник . Мн. Беларусь, 1991

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.