1. РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ СХЕМЫ ЦИФРОВОГО ИНТЕГРИРУЮЩЕГО РЕГУЛЯТОРА

Основным элементом цифрового интегрирующего регулятора является блок счётчиков. Который осуществляет счёт импульсов, т.е. преобразования числа импульсов в код, чтобы этот код далее преобразовать в напряжение. Так как при счёте импульсов код числа изменяется постепенно, с шагом 1, то можно получить постепенное нарастание и спад кода, а значит и выходного напряжения. Так как напряжение на входе может быть двухполярным, то блоков счётчиков должно быть два. Один блок счётчиков для положительного входного напряжения, а другой – для отрицательного. Полярность входного сигнала будет определяться компаратором.

Счётчик считает импульсы. А на входе схемы поступает напряжение, поэтому необходимо на вход поставить преобразователь (напряжение – частота).

Для управления работой счётчиков необходим блок управления (БУ).

Функции блока управления:

- В зависимости от полярности входного напряжения, определяет направление счёта (положительное или отрицательное приращение).

- При переполнении счётчиков выполняет его блокировку.

Блок управления счётчиками состоит из устройства хранения информации (П) на основе D-триггеров, формирователя сигнала блокировки (ФСБ) и схемы определения нуля (СОН).

Для преобразования цифрового кода в аналоговый сигнал используют ЦАП.

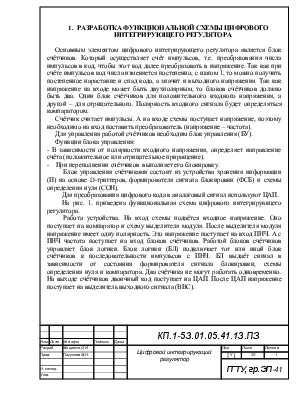

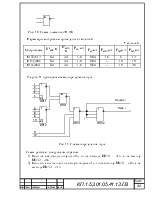

На рис. 1. приведена функциональная схема цифрового интегрирующего регулятора.

Работа устройства. На вход схемы подаётся входное напряжение. Оно поступает на компаратор и схему выделителя модуля. После выделителя модуля напряжение имеет одну полярность. Это напряжение поступает на вход ПНЧ. А с ПНЧ частота поступает на вход блоков счётчиков. Работой блоков счётчиков управляет блок логики. Блок логики (БЛ) подключает тот или иной блок счётчиков к последовательности импульсов с ПНЧ. БЛ выдаёт сигнал в зависимости от состояния формирователя сигнала блокировки, схемы определения нуля и компаратора. Два счётчика не могут работать одновременно. На выходе счётчиков двоичный код поступает на ЦАП. После ЦАП напряжение поступает на выделитель выходного сигнала (ВВС).

Рис. 1. Функциональная схема цифрового интегрирующего регулятора

Обозначения на схеме:

ПНЧ – преобразователь напряжение – частота;

БС – блок счётчиков;

ЦАП – цифро-аналоговый преобразователь;

ФСБ – формирователь сигнала блокировки;

СОН – схема определения нуля;

ВВС – выделитель выходного сигнала;

БИ – блок индикации.

2. РАСЧЁТ ОТДЕЛЬНЫХ УЗЛОВ И ОСНОВНЫХ ЭЛЕМЕНТОВ СХЕМЫ ЦИФРОВОГО ИНТЕГРИРУЮЩЕГО РЕГУЛЯТОРА

2.1. Расчёт ПНЧ

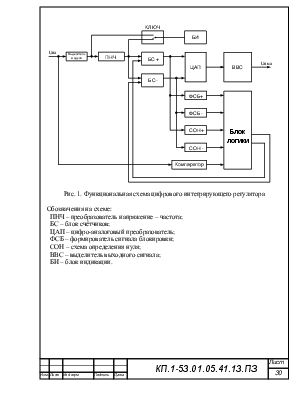

В качестве ПНЧ выбираем микросхему КР1108ПП1, которая может работать в качестве преобразователя напряжения – частота.

Рис. 2. Функциональная электрическая схема АЦП ИС КР1108ПП1 в режиме ПНЧ

Кристалл ИС изготавливается по биполярной технологии и размещается в 14-выводном герметичном пластмассовом корпусе типа 201.14-2 с двухрядным вертикальным расположением выводов.

Микросхема содержит все необходимые для ПНЧ узлы, включая встроенный ИОН.

Назначение и нумерация микросхемы: 1- инвертирующий вход; 4- напряжение источника питания Ucc1; 5-ёмкость одновибратора; 7- частотный выход; 10-выход КН; 11- общий; 12- напряжение источника питания Ucc2; 13- аналоговый выход; 14- неинвертирующий вход; 2,3,6,8,9 - незадействованные выводы.

Погрешность линейности преобразования в частотном диапазоне 5 Гц – 10 кГц не

превышает 0,01% при изменении рабочих температур от -10 до +70 ![]() .

.

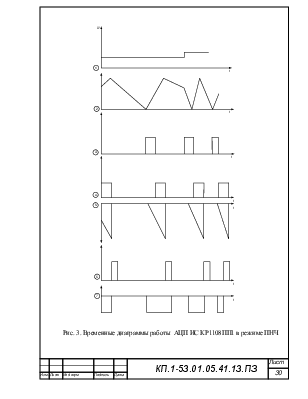

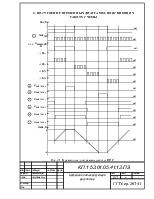

Рис. 3. Временные диаграммы работы АЦП ИС КР1108ПП1 в режиме ПНЧ

Основные электрические

параметры микросхемы при температуре окружающей среды 25![]() 10

10![]() , в диапазоне частот

(0,01-10) кГц

, в диапазоне частот

(0,01-10) кГц ![]() 1Гц,

диапазоне напряжений (0-10) В

1Гц,

диапазоне напряжений (0-10) В ![]() 0,1%

приведены в таблице 1.

0,1%

приведены в таблице 1.

Таблица 1.

|

Не менее |

Не более |

|

|

Напряжение смещения нуля на входе UI0 ,мВ |

-4 |

4 |

|

Входной ток смещения нуля по инвертирующему входу II02, нА |

-8 |

12 |

|

Входной ток смещения нуля по неинвертирующему входу II01, нА |

– |

60 |

|

Выходное напряжение низкого уровня U0L, В |

– |

0,4 |

|

Токи потребления ICC1 , ICC2 , мА |

– |

5,5 |

Предельно допустимые и предельные электрические режимы эксплуатации приведены в таблице 2.

Частоты генерируемых выходных или воспринимаемых входных импульсов

ИС КР1108ПП1 устанавливаются с помощью внешних элементов и могут изменяться в диапазоне от долей Герц до 500 кГц. Частота выходных импульсов в режиме ПНЧ приближённо определяется из соотношения:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.