6. Общая хар-ка PIC16F87X:

1) высокоскор. RISC-архитектура

2) 35 команд

3) Fтакт 0-20Мгц

4) сторожевой таймер с собств.

RS-генератором

5) сброс по включению питания

6) таймер сброса PWRT

7) таймер ожидания запуска генератора после включения питания

8) режим внутрисхемной отладки

9) широкий диапазон Uпит. От 2 до 5.5В

10) высокая нагрузочная способность портов ввода/вывода до25мА

11) малое энергопотребление

12) широкий набор периферийных модулей

Основные параметры:

1) FLASH-память программ

2) Память данных(байт)

3) EEPROMданных (байт)

4) Число источников прерываний

5) Порты ввода/вывода

6) Модуль 10-разрядного АЦП

7) Корпус (кол-во выводов)

Организация памяти программ:

3 вида памяти: 1) ПП (типа FLASH )

2) ПД (АЗУ)

3) EEPROM (ПД)-8к-слов

INDF-признак косвенной адресации.

INTCON-регистр управления прерываниями:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

GIE |

PEIE |

TOIE |

INTE |

RBIE |

TOIF |

INTF |

RBIF |

GIE=1-все прерывания разрешены

PEIE-разрешен. прерываний от периферийных устройств (=1-разрешены).

Запись и чтение EEPROMданных и FLASH-память программ:

Используется 6 регистров спец. функций:

![]()

![]() EEDATA регистр

данных EECON1 регистр

управления

EEDATA регистр

данных EECON1 регистр

управления

EEDATH EECON2

![]() EEADR регистр

адреса

EEADR регистр

адреса

EEADRH

Запись/чтение EEPROMданных: в EEADR 128-бит EEPROM. Старший бит =0.

Запись/чтение FLASH-память программ - программа приостанавливается при записи и чтении

EEADRH – старший байт

EEADR – младший байт

8. МК семейства PIC17:

PIC17CXXX – семейство высокопроизводительных микроконтроллеров с расширенной системой команд 16-разрядного формата (58 команд), работающие на частоте до 33 МГц, с объемом памяти программ до 16 Кслов. Кроме обширной периферии, 16-уровневого аппаратного стека и векторной системы прерываний, почти все микроконтроллеры этого семейства имеют встроенный аппаратный умножитель 8х8, выполняющий операцию умножения за один машинный цикл. Являются одними из самых быстродействующих в классе 8-разрядных микроконтроллеров;

2 подсемейства:

PIC17С4X

1) Память до 8 кило-слов,

2) EEPROM-многократно

программируемые с элементами стирания

3) 33 канала ввода/вывода

4) до 454 байт памяти данных

5) 4 таймера-счётчика (2 8ми-разрядных и 2 16ти-разрядных)

PIC17С75X

1) ПП до 16 кило-слов,

2) до 902 памяти данных,

3) 4 таймера-счётчика,

4)10 разрядный многоканальный АЦП,

5) 50 каналов ввода/вывода

Возможна работа с внешней памятью программ, существует 4 режима:

1) Режим микропроцессора

2) Р-м микроконтроллера

3) Расширенный МК (предоставляет доступ к внутренней и внешней ПП, переключение происходит автоматически.)

4) Защищённый МК (может устанавливать защиту от чтения кода)

Р-м микроконтроллера и защищённый МК предусматривает работу только с внутренней ПП. 64 кслов ПП.

9. МК семейства PIC 18: общая хар-ка, основные параметры, организация памяти программ и данных, банк доступа.

Микроконтроллеры семейств PIC компании объединяют все передовые технологии микроконтроллеров: электрически программируемые пользователем ППЗУ, минимальное энергопотребление, высокую производительность, хорошо развитую RISC-архитектуру, функциональную законченность и минимальные размеры. Широкая номенклатура изделий обеспечивает использование микроконтроллеров в устройствах, предназначенных для разнообразных сфер применения.

Высокая скорость выполнения команд в PIC-контроллерах достигается за счет использования двухшинной гарвардской архитектуры. Гарвардская архитектура основывается на наборе регистров с разделенными шинами и адресными пространствами для команд и данных. Все ресурсы микроконтроллера, такие как порты ввода/вывода, ячейки памяти и таймер, представляют собой физически реализованные аппаратные регистры.

Микроконтроллеры PIC содержат RISC-процессор с симметричной системой команд, позволяющей выполнять операции с любым регистром, используя произвольный метод адресации. Пользователь может сохранять результат операции в самом регистре-аккумуляторе или во втором регистре, используемом для операции.

1. Производительность 10 MIPS

2.Получение кодов, удобных для написания на языке Си.

3. Получит коды, которые совместимы с ранее выпускаемыми семьями.

Основные хар-ки.

1.Процессорное ядро:

· Набор команд оптимизированных под компилятор Си 175 команд

· Машинный код совместим с PIC 16 и 17

· Линейная адресация программной памяти

· Линейная адресация памяти данных

· Производительность 10

· 8-разрядные данные и 16-разрядные команды

· Приоритетные векторные системы прерываний

2. Передаточные устройства:

· Нагрузочная способность линии ввода/вывода 25мА

· Таймеры

Таймер 0 (счетчик 8 или 16 бит) с 8-разрядным предделителем

Таймер 1 (16 бит)

Таймер 2 (8 бит +рег. периода ШИН)

Таймер 3 (16 бит)

· два модуля сравнения захвата ШИН (2 ССР)

·

модуль синхрон. последоват. порта (MSSP)

в двух режимах: SPI и ![]() C

C

· универсал. синхр.-асинх. интерфейс (USART)

· параллельный интерфейс PSP

· 10-разрядный АЦП(многоканальный)

· WDT-таймер

· SLEEP-режим

· PLVD

- программный датчик по падению ![]()

· BOR

– программный сброс по падению ![]()

· широкий

диапазон ![]() : от 2.5 до 5.5 В

: от 2.5 до 5.5 В

· широкий диапазон рабочей температуры: от -40° до +125 ° С

Система обозначений:

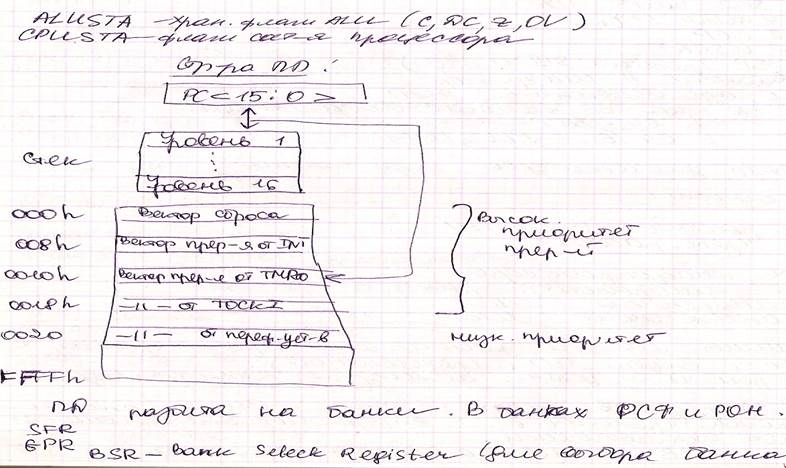

Организация памяти:

3 вида:

1.Память программ

2. Память данных

3. EEPRom- данных

PC ![]()

1)Память программ

|

PC<20:0> |

![]()

![]()

|

Уровень 1 |

|

|

Стек (команд) |

. . . |

|

Уровень 31 |

|

|

Вектор сброса |

|

0018h |

Вектор прерывания с высоким приоритетом |

|

|

|

|

|

Вектор прерывания с низким приоритетом |

|

3FFFh FFFFh |

|

|

Чтение как 0 |

252/452

242/442

для PIC 18 C 242/442 0000h -3FFFh

для PIC 18 C 252/452 000h –FFFFh

≥ 200 000h – для записи слова конфигурации и номера идентификации

2) Память данных

В виде массива 8-разр. ячеек (регистры) ОЗУ

4096 – регистров

12-разр. адрес

16 банков по 256 регистров

GPR (РОН)

SER (PCT) только в 15 банке

ВSR <3:0>

|

080h

|

ОЗУ быстрого доступа |

00h |

|

GPR |

FFh |

|

|

100h 1FFh |

GPR |

00h FFh |

|

|

. . . |

00h |

|

F7Fh F80h |

Не используется |

|

|

|

SFR |

FFh |

BSR (банк выбора регистра ) использ. только младшую тетраду

Если а=1, то исп-ся ВSR

а=0, то исп-ся банк доступа

MOVLB K, K →(BSR)

MOVLB 0×01; Выбор 1-го банка

12-разр. адрес

BSR <3:0>

|

3 |

0 |

7 |

команды |

0 |

|||

|

….. |

|

|

00h |

01h |

0Fh |

||

|

000h 0FFh |

100h FFh |

F00h FFFh |

||

|

б.1 |

б.2 |

б.15 |

||

BSR xxxx 0000 – 0-й банк загруж. только младшая тетрада

xxxx 1111 – 15-й банк

MOVLB const; const→ (BSR)

MOVLB 0×01; выбор 1-го банка или MOVLB 3'0001'

“-“ прямой адресации: указывает адрес регистра

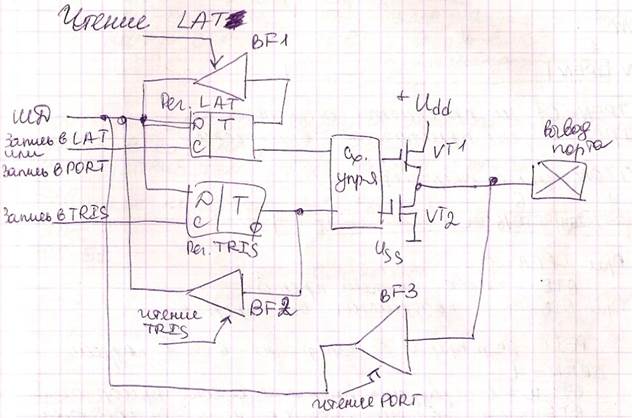

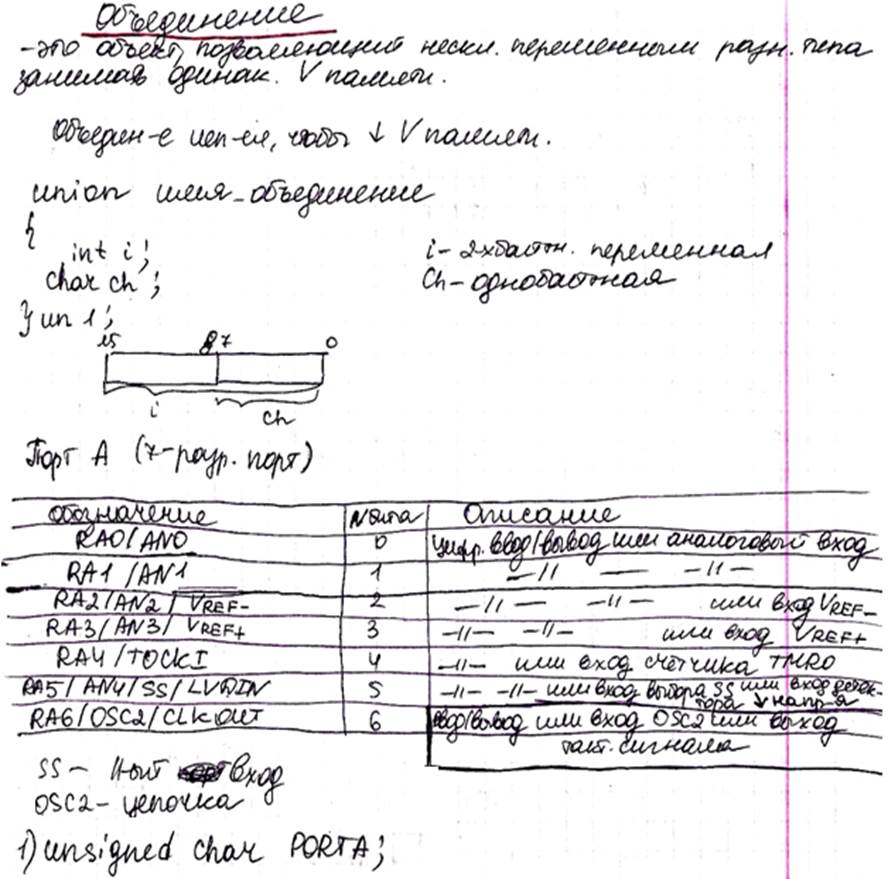

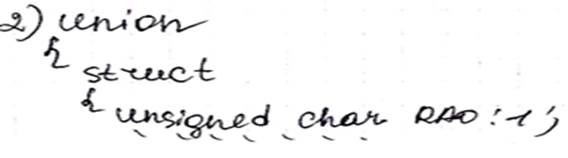

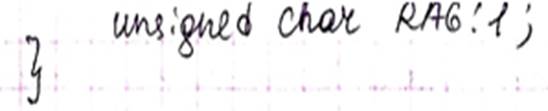

11. МК семейства PIC18: порты ввода-вывода, стек и его разновидности.

“Чтение – модификация – запись”

Каждую порту соответствуют 3 регистра

1. TRIS – регистр выбора направления передачи данных

PORT – регистр порта (реал. лог. уровни на выводах)

|

Инициализация порта А RA0, RA1, …RA6

CLRF PORTA; очистить триггеры PORTA

или

CLRF LATA, 0; очистить триггеры LATA

MOVLW 0×CF; в регистр WREG записать B’11001111’

MOVWF TRISA, 0; настроить линии RA (0,1,2,3,6) на ввод; линии RA (4,5) на вывод.

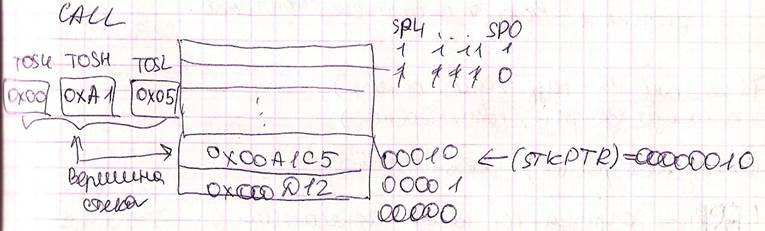

Стек МК.

31 ячейка памяти разрядность ячейки: 21 бит

Для сохранения адреса возврата при вызове п/п.

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

STKFUL |

STKUNF |

- |

SP4 |

SP3 |

SP2 |

SP1 |

SP0 |

|

R/C - 0 |

R/C - 0 |

R- 0 |

|

R/W - 0

STKFUL – переполнения если=1, то стек полон или переполнен если STKUNF=1, то стек исчерпан

TOS U – верхн.рег.

TOS H – cт.рег.

TOS L – мл.рег.

TOS

– имя вершины стека

Быстрый стек.

Использ. при обработке прерываний с высоким приоритетом

RETFIE, CALL, RETURN

Если FAST=1, то используется быстрый стек.

CALL SUBR, 1; вызов п/п с сохранением сод-го WREG, STATUS, BSR в быстром стеке

.

.

.

SUBR ; п/п SUBR

…..

…..

RETURN 1; возврат с восстановлением контекста

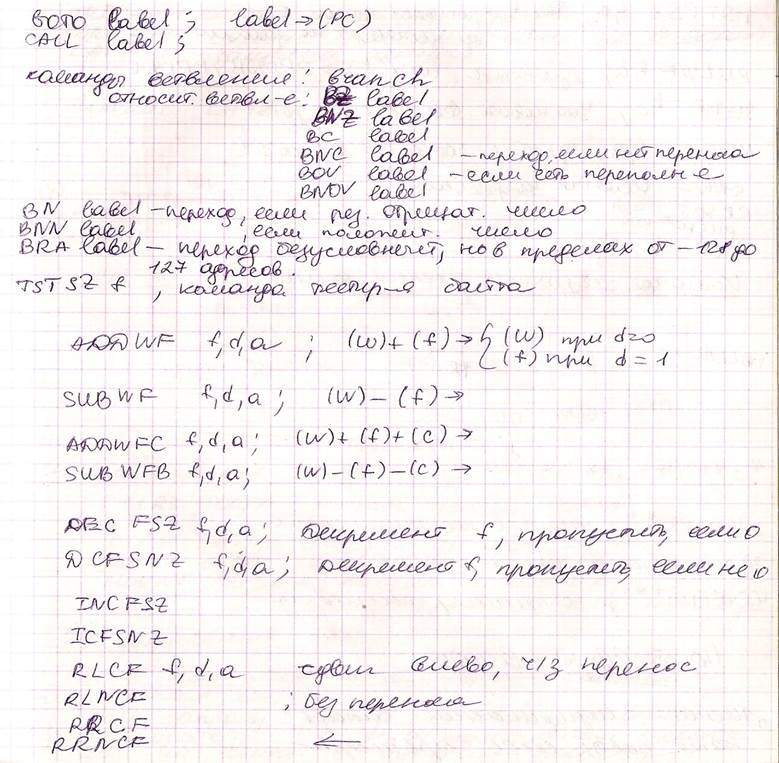

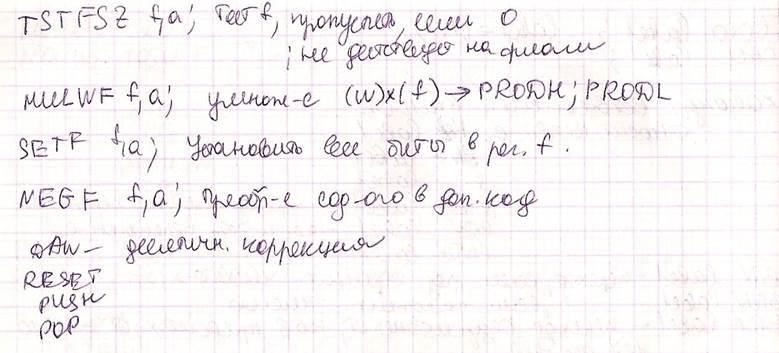

10. МК семейства PIC18: особенности системы команд.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

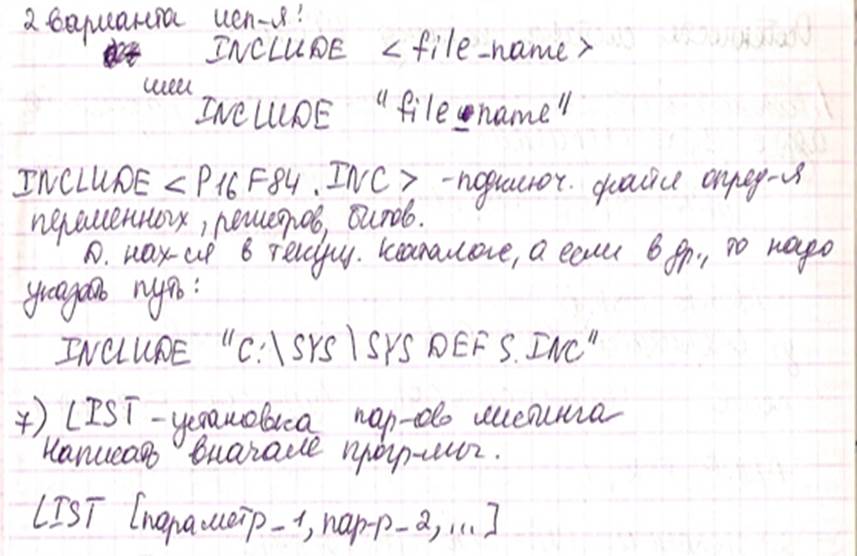

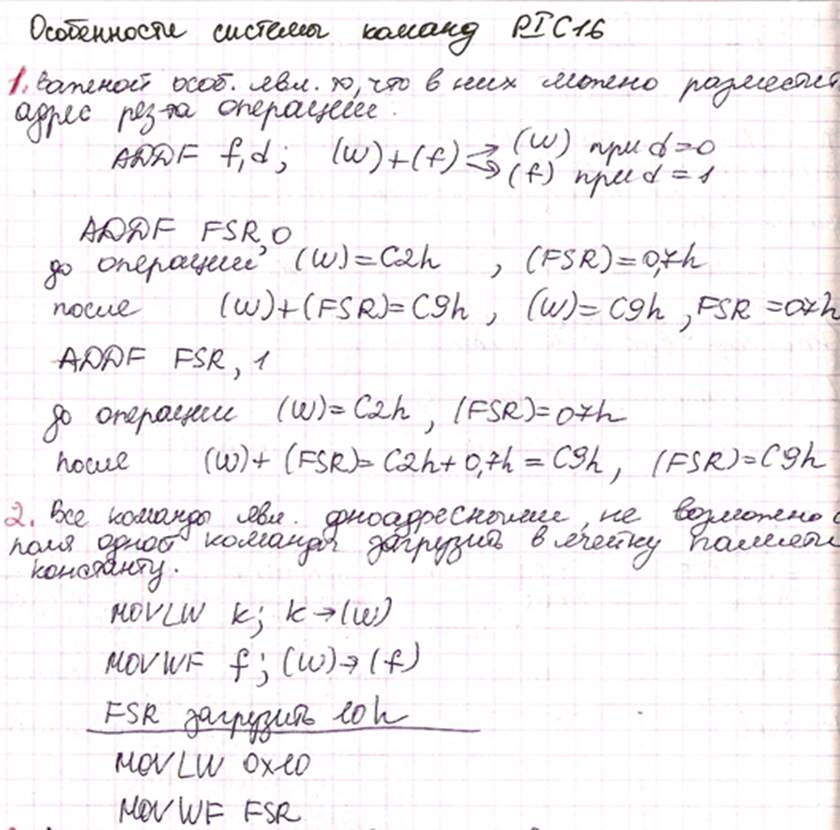

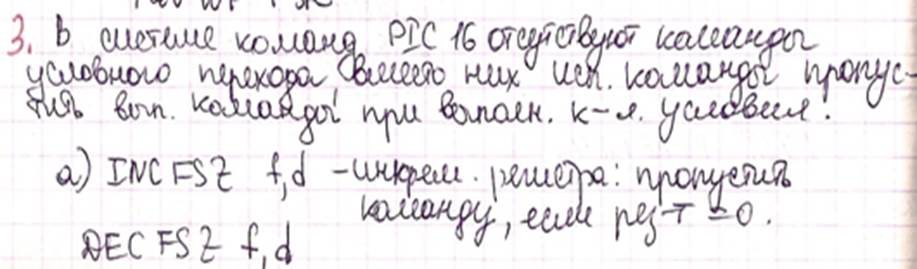

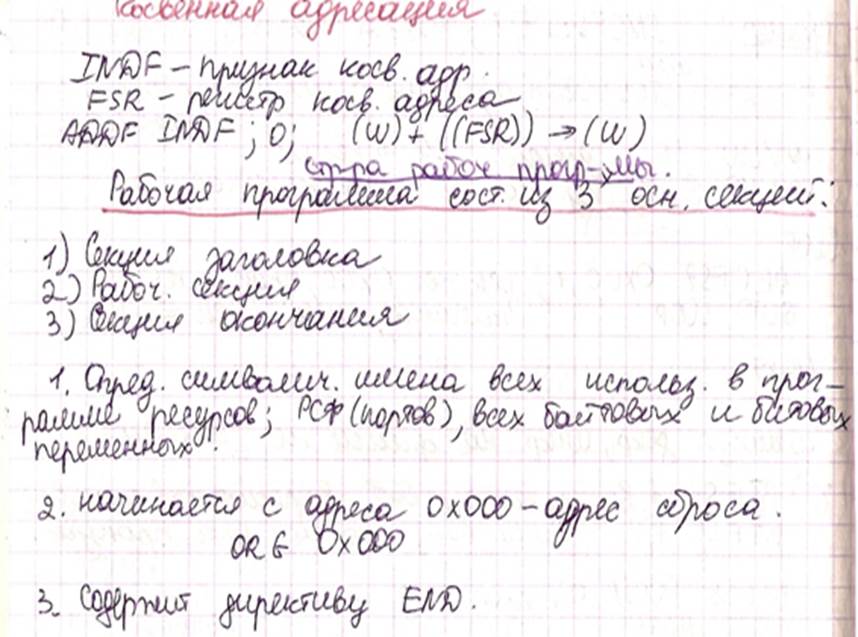

1. Система команд МК PIC16F84 общая характеристика. Прямая и косвенная адресация.

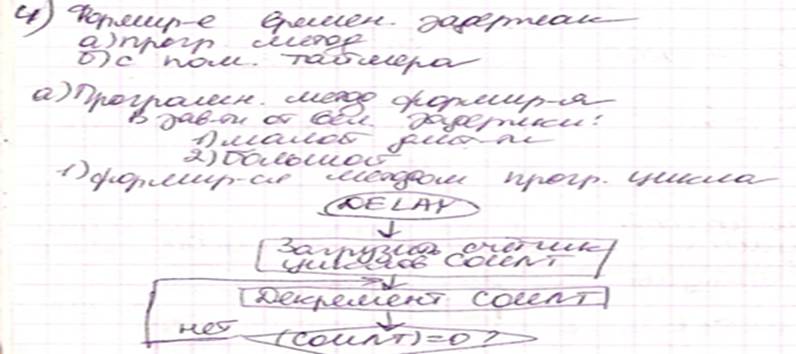

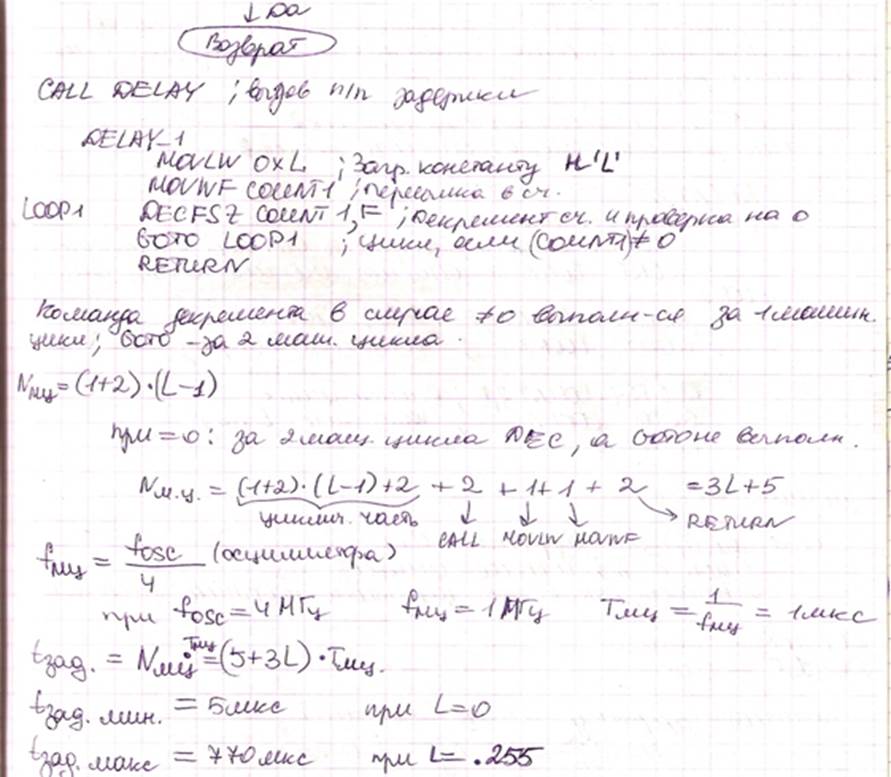

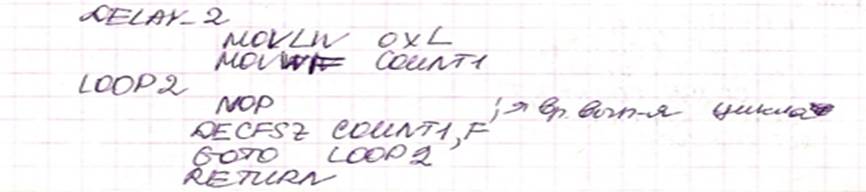

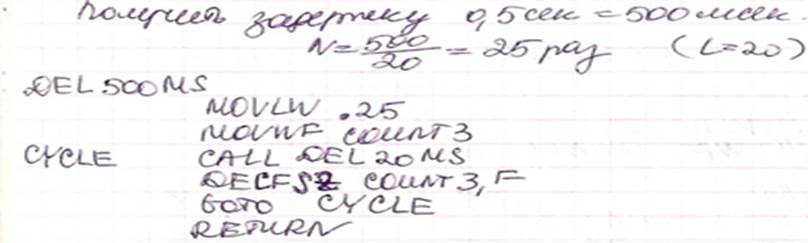

3.Реализация временных задержек

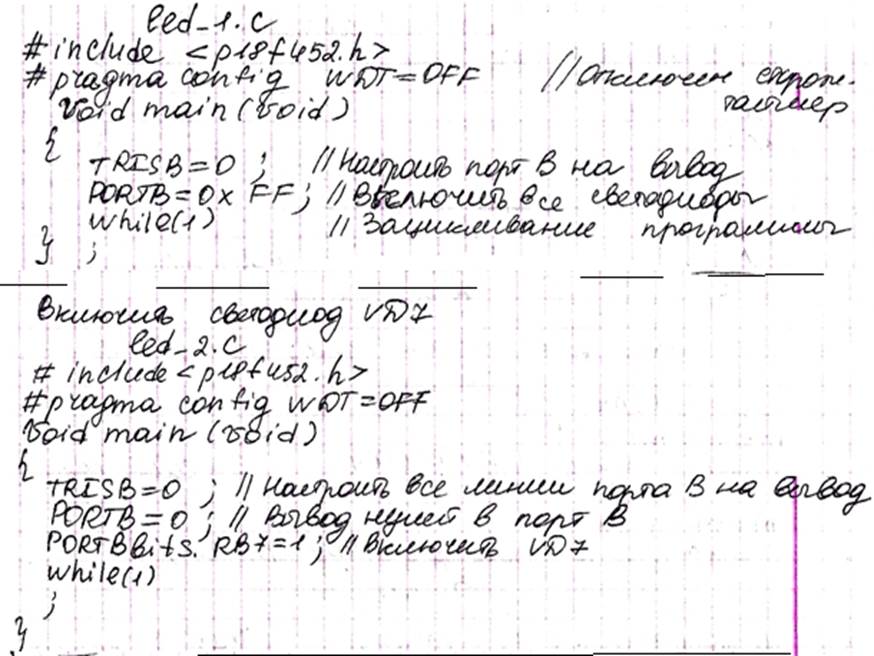

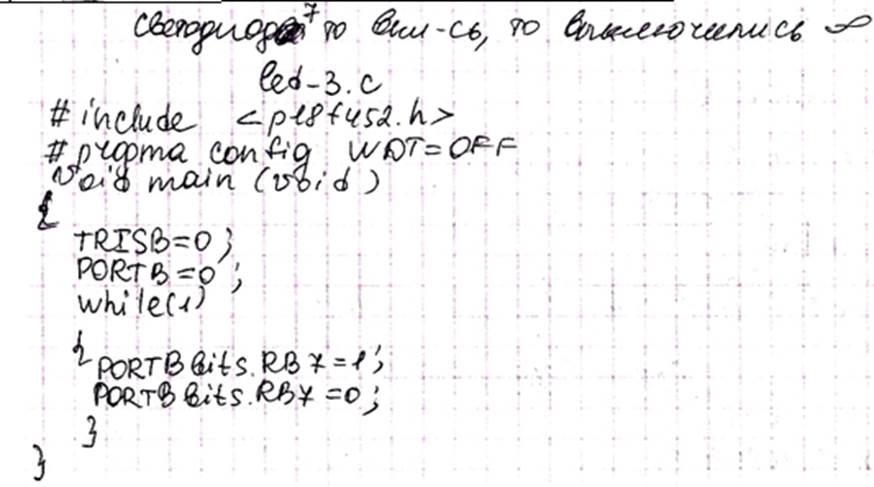

19.Пример программы для С18 управление светодиодами(включение-- выключение)

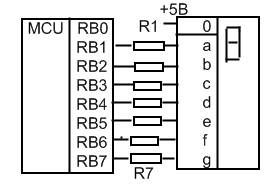

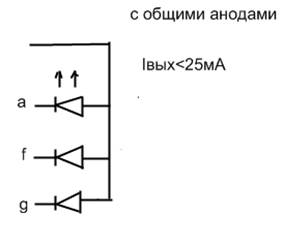

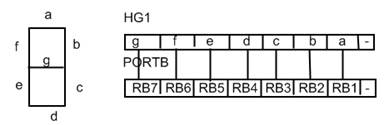

4. Программирование

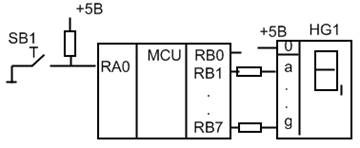

упр. светодиодом и семисегментным индикатором:

“светятся”, где 0

Семисегментный код

Двоичный HEX- код

1000 0000 0х80

1111 0010 0хF2

…………. …..

0001 1100 0x1C

; SEVEN_SEG – п/п перекодировки

; входной параметр – рег. W – двоичный (позиционный) код символа (HEX-код)

; выходной параметр – рег. W –семисегментный код (HEX-код)

SEVEN_SEG

ANDLW 0x0F; Маскирование ст. тетрады рег.W

ADDWF PCL, F; Cложение рег.W и PCL (прогр. счетчик)

RETLW 0x80; возврат с W= 0x80

RETLW 0xF2; возврат с W=0xF2 (символ “1”)

RETLW 0x1C; возврат с W=0x1С (символ “F”)

; Программа вывода на индикатор

; Вх. Параметр – рег. W – двоичн. (HEX-код) символа

OUTP_HG

CALL SEVEN_ SEG; п/п перекодировки

MOVWF PORTB; Вывод в PORTB

RETURN

CALL OUTP_HG

TEMPA EQU 0x10

COUNT EQU 0x1C ; (Счетчик кол-ва нажатий)

CLRF COUNT ; очистить счетчик COUNT

CALL OPROS_RA0 ; п/п опроса RA0

BTFSC TEMPA, 0 ; тестирование линий RA0

Пропустить, если RA0=0 (SB1 нажата)

GOTO WAIT ; цикл ожидания

INCF COUNT, F ; инкремент счетчика

MOVF COUNT,W ; пересылка COUNT в рег. W

CALL SEVEN_SEG ; п/п перекодировки

MOVWF PORTB ; вывод на индикатор

BTFSS TEMPA, 0 ; если RA0=1, то пропустить команду

GOTO TEST ; цикл отжатия кнопки SB1

GOTO AGAIN

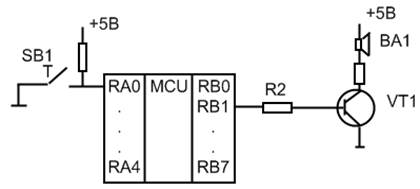

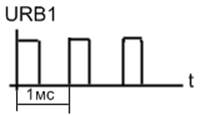

Формирование звукового сигнала

f=1кГц

f=1кГц

При нажатии на кнопку должен включиться динамик.

ORG 0x000

CALL INIT_PORTS

AGAIN

CALL OPROS_RA0 ; П/п опроса RA0

CALL SB1_BA1 ; П/п звука

GOTO AGAIN

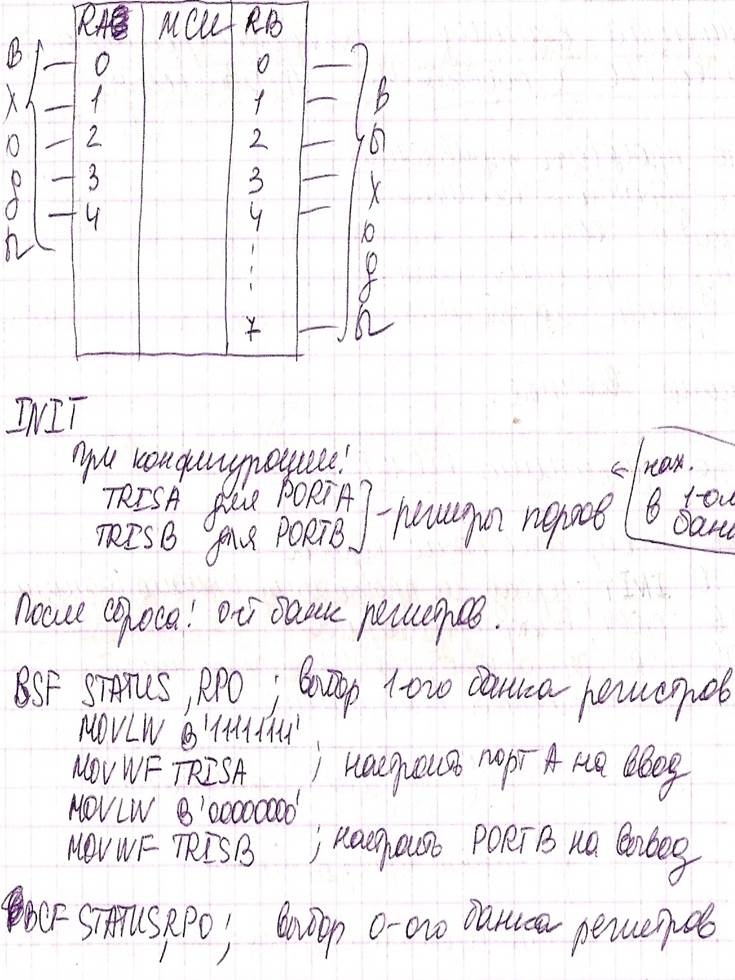

INIT_PORTS

BSF STATUS RP0 ; Выбор BANK1

MOVLW 0xFF

MOVWF TRISA ; Настроить PORTA на ввод

CLR W ;Cбросить регистр W

MOVWF TRISB ;Настроить PORTB на вывод

BCF STATUS, RP0 ;Выбор BANK0

BCF PORTB, 1 ;Вывести RB1=0

RETURN

TEMPA_

SB1_VD1 ; П/п звука на BA1

BTFSC TEMPA,0 ;пропустить команду, если SB1 нажата

GOTO MET

BSF PORTB,1 ;Вывод RB1=0

CALL DEL 500MKS ;задержка на 500мкс

BCF PORTB,1 ;Вывод RB1=0

CALL DEL 500MKS;

MET

RETURN ; Возврат из п/п

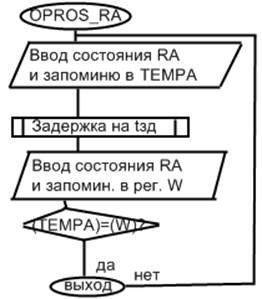

Опрос состояния кнопки и переключателя

OPROS_RAO

MOVF PORTA, W ; пересылает из PORTA в W

ANDLW B ‘0000 0001’ ; выделить 0-й разряд

MOVWF TEMPA ; Пересылка в TEMPA

CALL DEL 20MS ; Задержка на 20 мс

MOVF PORTA, W ; пересылка из PORTA в W

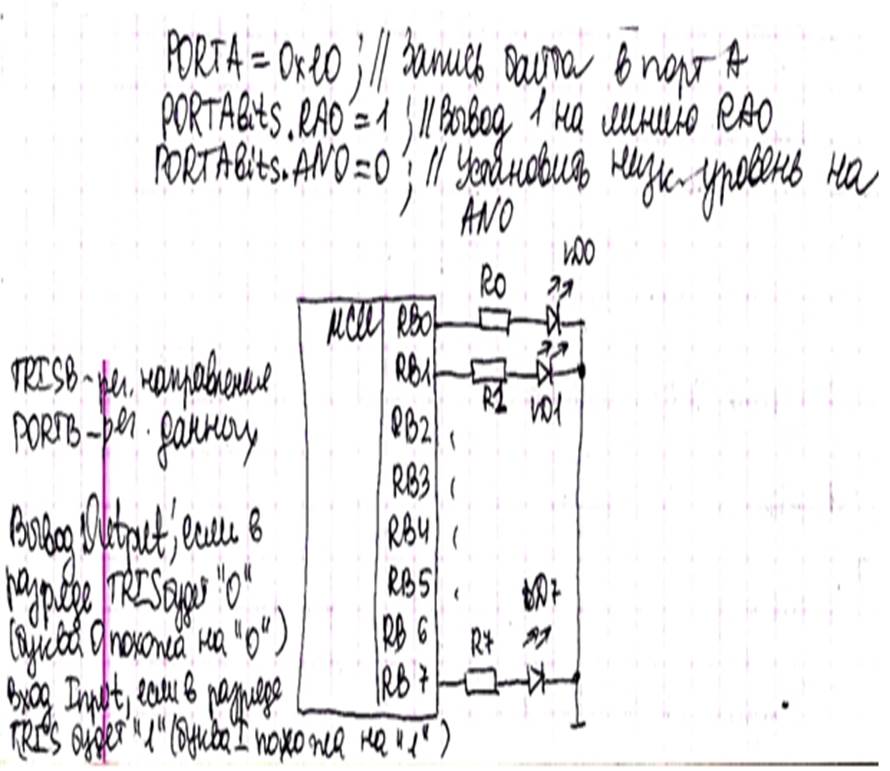

5. Двунаправленный порт ввода/вывода PORTB.

7.МК семейств PIC16F87x состав периферийных модулей и модуль АЦП:

- таймер 0 (TMR0) : входит 8-ми разрядный таймер-счётчик.

- таймер 1 (TMR1) : входит 16-ти разрядный таймер-счётчик с возможностью подключения внешнего резонатора.

- таймер 2 (TMR2) : входит 8-ми разрядный таймер-счётчик с 8-ми разр. предварительным делителем и выходным делителем.

- 2 модуля : CCP1,CCP2-модули захвата/сравнения/ШИМ. 16-ти разр. захват/16-ти разр. сравнение/10-ти разр. ШИМ.

- модуль многоканальн. 10-ти разр. АЦП (5 или 8 каналов).

- последовательный синхронно-асинхронный приёмо-передатчик USART.

- модуль последовательного синхронного порта MSSP.

Модуль 10-ти разр. АЦП:

5 каналов для МК в 28- выводном корпусе и 8 – в 40-выводн. корпусе.

ADRESH-регистр результата (старший байт кода АЦП)

ADRESL-мл. байт

ADCON0, -регистр управления

ADCON0:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

ADCS0 |

CHS2 |

CHS1 |

CHS0 |

GO/DONE |

----- |

ADON |

Выбирает источник тактового сигнала для работы с АЦП .

Если режим АЦП SLEEP, нужен внутренний тактовый генератор Frc.

GO/DONE-бит запуска АЦП (=1-начинается преобразование; =0-преобр

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.