Дополнительная информация

1. Bosch. САМ specification. Version 2.

2. Сайт фирмы Bosch,

3. Сайт «Рынок микроэлектроники». Спецификации CAN и статьи по-русски.

4. Интерфейсы открытых систем: Учебный курс.

5. Новинки элементной базы,

3.4. Внутримодульный интерфейс 12С

Интерфейс PC, видимо, самый лаконичный и простой последовательный интерфейс передачи данных. Стандарт разрабатывался для обмена данными между БИС в пределах одной печатной платы. Первоначальное назначение - тестирование и инициализация БИС. Поскольку подсистемы тестирования не могут составлять более 20 % от рабочей аппаратуры, в интерфейсе PC нет ничего лишнего — только то, без чего нельзя обойтись. Реализация линий передачи данных и общая идеология обмена данными напоминают интерфейс CAN. Отсюда и схожесть положительных черт: малые затраты времени на системные операции, удобный арбитраж и организация механизма приоритетов, дешевизна реализации линий обмена данными.

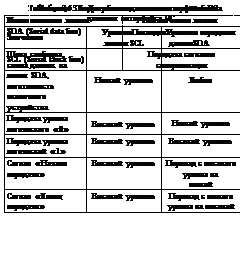

Интерфейс PC базируется всего на двух линиях передачи данных. Они построены одинаково, по схеме «монтажного И» (см. раздел 3.3 об интерфейсе CAN). Буферные схемы линий могут быть легко реализованы в любой современной технологии изготовления микросхем. Выходные ключи — по схеме с открытым эмиттером (затвором). Входные каскады обычно строятся по схеме триггера Шмидта. Обе линии являются двунаправленными. Информацию на них в ходе обмена данными могут выдавать как контроллер, так и оконечное устройство. Любой порт может становиться контроллером, если в его структуре заложена такая функция (табл. 3.5).

На линии обмена

данными допустимы состояния, перечисленные в табл. 3.6.

|

Передачу начинает любой порт (рис. 3.15). Он выставляет высокий уровень на линии SCL, а на линии SDA формирует сигнал «Начало передачи». Он представляет собой перепад, во всех других случаях воспринимаемый как сбой. Порт, передавший сигнал «Начало передачи», считает себя контроллером, захватившим управление интерфейсом. Он начинает передавать адрес оконечного устройства со старшего бита. Обычно адрес состоит из 7 битов. Восьмым битом передаётся признак направления пересылки данных. Уровень логического «О» означает передачу данных в оконечное устройство, уровень логической «1» - приём данных из оконечного устройства. После приёма каждого байта, в том числе адресного, приёмниквыдаёт сигнал подтверждения в виде уровня логического «О» на линии SDA. Подтверждение приёма адресного байта означает опознавание оконечным устройством своего адреса. Если при этом оконечное устройство не готово начать обмен данными, оно фиксирует уровень логического «О» на линии SLC. Поскольку линия построена по схеме «монтажного И», этот уровень будет оставаться на линии, пока оконечное устройство его не снимет. Этим механизмом обеспечивается функционирование асинхронного режима обмена данными. Аналогично он работает и при приёме каждого бита данных. При отсутствии задержек, вносимых оконечным устройством, скорость передачи составляет 100 кбит/с.

Передача данных в том или ином направлении осуществляется под управлением положительных синхронизирующих импульсов на линии SLC, формируемых контроллером. После передачи каждого байта вставляется байт подтверждения, свидетельствующий о безошибочном его приёме. В конце операции обмена данными контроллером формируется сигнал «Конец передачи».

Арбитраж функционирует аналогично интерфейсу CAN. Если несколько портов одновременно пытаются захватить управление, они формируют одинаковые

стартовые сигналы и начинают передавать адресный байт. Все передающие порты контролируют реальный уровень сигнала на линии SDA. Схема «монтажного И» исключает шинные конфликты в гакой ситуации, но в тот момент, когда разные порты выдают в линию SDA одновременно уровни логического «0» и логической «1», превалирующий логический «0» присутствует на шине (за счёт «монтажного И»). Порт, выставивший уровень логической «1», но обнаруживший уровень логического «0» на линии SDA, считает себя проигравшим процедуру арбитража. Таким образом, сообщение с численно меньшим адресом считается более приоритетным. Обнаружив эту ситуацию, порт, передавший уровень логической «1», прекращает передачу и немедленно переходит в режим приёма. Далее он работает как обычный порт, начавший приём адресного байта с самого начала обмена данными, и может оказаться адресуемым оконечным устройством. В случае трёх и более одновременно захватывающих шину портов арбитраж происходит аналогично. При совпадении адресного байта процедура арбитража продолжается с байтами данных, следующих за ним.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.