Это регистр управления функционированием FIFO. Он определяет стартовый адрес FIFO и количество зарезервированных буферов сообщений в DMA RAM (См Регистр 18). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL<0>=0).

CiFIFO регистр статуса FIFO

Этот регистр состоит из указателей чтения и записи. Указатель записи показывает который буфер самый последний принял данные. Указатель чтения говорит пользователю какой буфер читать следующий (См регистр 19). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL<0>=0).

3.5 Регистры управления/состояния прерывания

CiINTF регистр флагов прерывания

Этот регистр показывает состояние различных источников прерывания ECAN модуля (См регистр 20). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL<0>=0).

CiINTE регистр разрешения прерываний

Этот регистр используется для выборочного включения/выключения прерывания от 7 основных источников прерываний: прерывание передающего буфера, прерывание приемного буфера, переполнение приемного буфера, прерывание FIFO почти полное, прерывание ошибки, прерывание пробуждения и прерывание по принятию ошибочного сообщения. (См регистр 21). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL<0>=0).

СiVEC: регистр кода прерывания

Этот регистр содержит биты кода прерывания которые могут быть использованы с векторами прерываний для эффективного использования прерываний (См регистр 22). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL<0>=0).

3.6 Регистры управления и счетом ошибок.

CiCTRL1: регитср управления 1

Этот регистр устанавливает режим функционирования ECAN модуля (См регистр 23). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL1<0>=0).

CiCTRL2: регистр управления 2

Этот регистр битов управления фильтрацией DeviceNet (См регистр 24). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL1<0>=0).

CiTRmnCON: регистр управления буферами m (m=0,2,4,6; n=1,3,5,7)

Эти регистры конфигурируют и управляют буферами сообщений (См регистр 25). Этот регистр доступен только если пользователь сбросил WIN бит (CiCTRL1<0>=0).

CiEC: регистр счетчика ошибок приема/передачи

Этот регистр считает ошибки чтения и передачи, Пользователь может считать этот регистр и определит текущее количество ошибок передачи и приема (См регистр 26).

CiRXD: регистр приема данных

Этот регистр временно задерживает каждое принятое слово. Этот регистр из которого DMA контролер считывает данные в DMA буфер.

CiTXD: регистр передачи данных

Этот регистр временно задерживает каждую передачу, Это регистр в который DMA контролер записывает данные из DMA буфера.

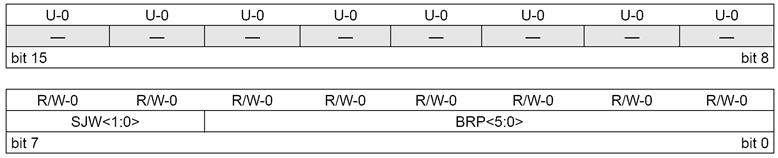

Регистр 1. CiCFG1: Регистр настройки скорости обмена ECAN

бит 15-8 Не реализовано: Читается как ‘0’

бит 7-6 SJW<1:0>: Synchronization Jump Width биты (биты ширины скачка синхронизации)

11 = Length is 4 x TQ

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = Length is 1 x TQ

бит 5-0 BRP<5:0>: биты предделителя скорости обмена

11 1111 = TQ = 2 x 64 x 1/FCAN

00 0010 = TA = 2 x 3 x 1/FCAN

00 0001 = TA = 2 x 2 x 1/FCAN

00 0000 = TQ = 2 x 1 x 1/FCAN

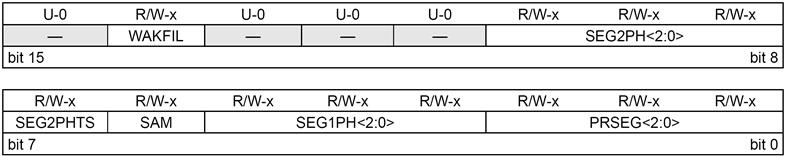

Регистр 2. CiCFG2: Регистр настройки скорости обмена ECAN

бит 15 Не реализовано: Читается как ‘0’

бит 14 WAKFIL: Выбор Фильтра линии шины CAN для Пробуждения

1 = использовать фильтр линии шины CAN для пробуждения

0 = фильтр линии шины CAN не используется для пробуждения

бит 13-11 Не реализован: Читается как ‘0’

бит 10-8 SEG2PH<2:0>: Phase Buffer Segment 2 bits

111 = Length is 8 x TQ

…………

000 = Length is 1 x TQ

бит7 SEG2PHTS: Phase Segment 2 Time Select bit

1 = Свободно программируемый

0 = Максимальный биты SEG1PH или Information Processing Time (IPT), какой из них больше

бит 6 SAM: Sample of the CAN bus Line bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.