AT25F4096 – микросхема памяти

Особенности

- Serial Peripheral Interface (SPI) Совместимый

- Поддерживает SPI Режимы 0 (0,0) и 3 (1,1)

- Даташит описывает Операцию Режима 0

- 33 МГЦ Тактовая частота

- Байтовый режим и 256-байтовый постраничный режим для программных операций

- Секторная архитектура:

- восемь секторов по 64 Кбит каждый (всего 4 Мбит)

- 256 Страниц в Секторе

- Режим идентификации устройства

- Низковольтные операции

- 2.7 (VCC = 2.7V к 3.6V)

- Секторная защита записи

- защищают 1/8, 1/4, 1/2 или весь объём

- Вывод Write Protect (WP) предназначен для аппаратной защиты данных, а инструкция Write Disable Instructions для программной защиты данных

- Время цикла программирования (обычно 30 мкс/байт)

- Время цикла стирания Сектора (Обычно 1 с/Сектор)

- Одиночный цикл перепрограммирования (Стирание и программирование) для регистра состояния

- Высокая надёжность

- выносливость: приблизительно 10 000 циклов записи

- Время хранения данных: 20 Лет

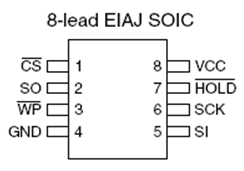

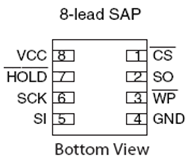

- 8-выводной EIAJ SOIC и 8-выводной Small Array Package (SAP)

Описание

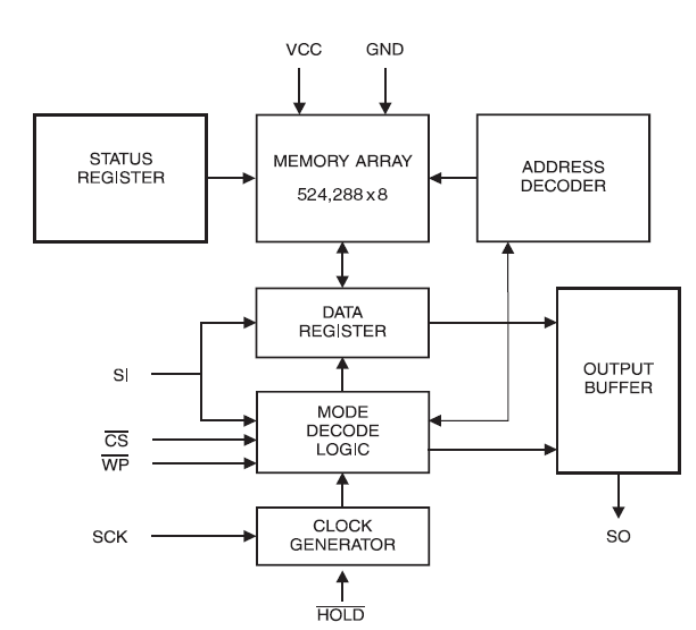

AT25F4096 содержит 4 194 304 бита последовательно перепрограммируемой Флэш-памяти, организованной как 524 288 слов 8 битов каждый. Устройство оптимизировано для использования во многих индустриальных и коммерческих приложениях, где необходимы низковольтное питание с низким энергопотреблением. AT25F4096 доступен в маленьком корпусе EIAJ с 8 выводами SOIC и 8-выводной корпус SAP.

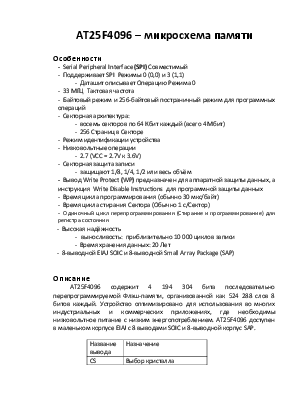

|

Название вывода |

Назначение |

|

CS |

Выбор кристалла |

|

SCK |

Вход тактовых импульсов |

|

SI |

Вход данных |

|

SO |

Выход данных |

|

GND |

Земля |

|

VCC |

Питание |

|

WP |

Защита от записи |

|

HOLD |

Приостанавливает Последовательный Ввод |

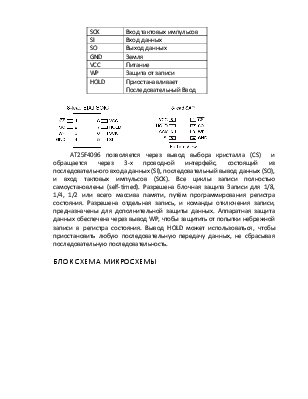

AT25F4096 позволяется через вывод выбора кристалла (CS) и обращается через 3-х проводной интерфейс, состоящий из последовательного входа данных (SI), последовательный вывод данных (SO), и вход тактовых импульсов (SCK). Все циклы записи полностью самоустановлены (self-timed). Разрешена блочная защита Записи для 1/8, 1/4, 1/2 или всего массива памяти, путём программирования регистра состояния. Разрешена отдельная запись, и команды отключения записи, предназначены для дополнительной защиты данных. Аппаратная защита данных обеспечена через вывод WP, чтобы защитить от попытки небрежной записи в регистра состояния. Вывод HOLD может использоваться, чтобы приостановить любую последовательную передачу данных, не сбрасывая последовательную последовательность.

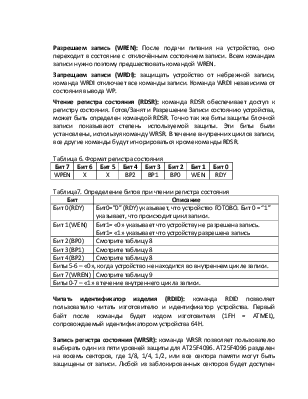

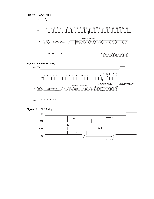

БЛОК СХЕМА МИКРОСХЕМЫ

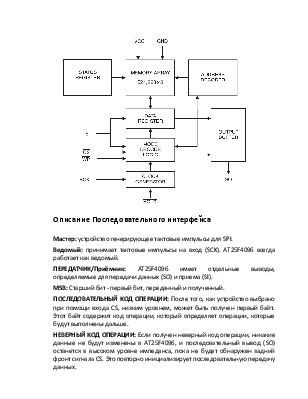

Описание Последовательного интерфейса

Мастер: устройство генерирующее тактовые импульсы для SPI.

Ведомый: принимает тактовые импульсы на вход (SCK). AT25F4096 всегда работает как ведомый.

ПЕРЕДАТЧИК/Приёмник: AT25F4096 имеет отдельные выводы, определяемые для передачи данных (SO) и приема (SI).

MSB: Старший бит - первый бит, переданный и полученный.

ПОСЛЕДОВАТЕЛЬНЫЙ КОД ОПЕРАЦИИ: После того, как устройство выбрано при помощи входа CS, низким уровнем, может быть получен первый байт. Этот байт содержит код операции, который определяет операции, которые будут выполнены дальше.

НЕВЕРНЫЙ КОД ОПЕРАЦИИ: Если получен неверный код операции, никакие данные не будут изменены в AT25F4096, и последовательный вывод (SO) останется в высоком уровне импеданса, пока не будет обнаружен задний фронт сигнала CS. Это повторно инициализирует последовательную передачу данных.

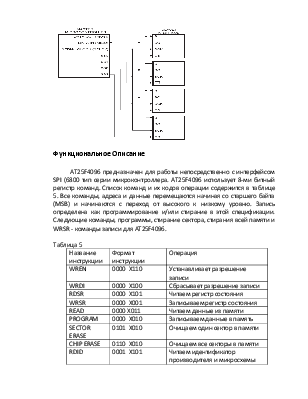

ВЫБОР КРИСТАЛЛА: AT25F4096 выбирается, когда на выход CS поступает низкий уровень. Когда устройство не выбрано, данные не будут приниматься через вывод SI, и вывод SO, на которых будет находиться состояние высокого импеданса.

УДЕРЖАНИЕ: вывод HOLD используется вместе с выводом CS, чтобы выбрать AT25F4096. Когда устройство выбрано, и осуществляется работа с данной микросхемой по SPI, то при помощи вывода HOLD можно приостановить последовательную передачу данных с МАСТЕР устройством, не сбрасывая последовательную последовательность. Чтобы сделать паузу, на вывод HOLD необходимо подать низкий уровень, в то время как на выводе SCK находится низкий уровень. Чтобы возобновлять последовательную передачу данных, на выход HOLD подаётся высокий уровень, в то время как выход SCK является низким (SCK, может все еще переключать в течение удержания). Вводы SI будет игнорироваться, в то время как, вывод SO находится в состоянии высокого импеданса.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.