ЗАЩИТА ЗАПИСИ: 25F4096 имеет особенность блокировки записи, которая может быть активизирована, при помощи вывода WP. Когда блокировка активизирована, блокированные сектора будут доступны только для чтения. Вывод защиты записи разрешает нормальные операции чтения/записи, когда на выводе высокий уровень. Когда на вывод WP подан низкий уровень, и бит WPEN - “1”, все операции записи для регистра состояния запрещены. Когда на WP подаётся низкий уровень, в то время как CS все еще имеет низкий уровень, то это прервет запись для регистра состояния. Если внутренний регистр состояния цикла записи уже инициализирован, то пришедший низкий уровень на вход WP не будет иметь никакого эффекта для любой операции записи регистра состояния. Функция вывода WP блокирована, когда бит WPEN в регистре состояния - “0”. Это позволит пользователю устанавливать AT25F4096 в систему с выводом WP, связанным с землёй и все еще способный записывать для регистра состояния. Все функции вывода WP разрешены, когда бит WPEN установлен в “1”.

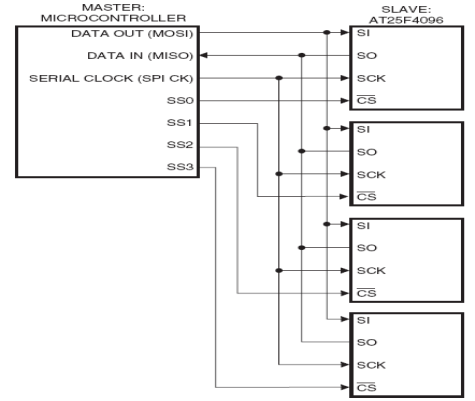

Схема подключения нескольких ведомых устройств

Функциональное Описание

AT25F4096 предназначен для работы непосредственно с интерфейсом SPI (6800 тип серии микроконтроллера. AT25F4096 использует 8-ми битный регистр команд. Список команд и их кодов операции содержится в таблице 5. Все команды, адреса и данные перемещаются начиная со старшего байта (MSB) и начинаются с переход от высокого к низкому уровню. Запись определена как программирование и/или стирание в этой спецификации. Следующие команды, программы, стирание сектора, стирания всей памяти и WRSR - команды записи для AT25F4096.

Таблица 5

|

Название инструкции |

Формат инструкции |

Операция |

|

WREN |

0000 X110 |

Устанавливает разрешение записи |

|

WRDI |

0000 X100 |

Сбрасывает разрешение записи |

|

RDSR |

0000 X101 |

Читаем регистр состояния |

|

WRSR |

0000 X001 |

Записываем регистр состояния |

|

READ |

0000 X011 |

Читаем данные из памяти |

|

PROGRAM |

0000 X010 |

Записываем данные в память |

|

SECTOR ERASE |

0101 X010 |

Очищаем один сектор в памяти |

|

CHIP ERASE |

0110 X010 |

Очищаем все секторы в памяти |

|

RDID |

0001 X101 |

Читаем идентификатор производителя и микросхемы |

Разрешаем запись (WREN): После подачи питания на устройство, оно переходит в состояние с отключённым состоянием записи. Всем командам записи нужно поэтому предшествовать командой WREN.

Запрещаем записи (WRDI): защищать устройство от небрежной записи, команда WRDI отключает все команды записи. Команда WRDI независима от состояния вывода WP.

Чтение регистра состояния (RDSR): команда RDSR обеспечивает доступ к регистру состояния. Готов/Занят и Разрешение Записи состоянию устройства, может быть определен командой RDSR. Точно так же биты защиты блочной записи показывают степень используемой защиты. Эти биты были установлены, используя команду WRSR. В течение внутренних циклов записи, все другие команды будут игнорироваться кроме команды RDSR.

Таблица 6. Формат регистра состояния

|

Бит7 |

Бит6 |

Бит5 |

Бит4 |

Бит3 |

Бит2 |

Бит1 |

Бит0 |

|

WPEN |

X |

X |

BP2 |

BP1 |

BP0 |

WEN |

RDY |

Таблица7. Определение битов при чтении регистра состояния

|

Бит |

Описание |

|

Бит 0 (RDY) |

Бит0=”0” (RDY) указывает, что устройство ГОТОВО. Бит 0 = “1” указывает, что происходит цикл записи. |

|

Бит 1 (WEN) |

Бит1= «0» указывает что устройству не разрешена запись. Бит1= «1» указывает что устройству разрешена запись |

|

Бит 2 (BP0) |

Смотрите таблицу 8 |

|

Бит 3 (BP1) |

Смотрите таблицу 8 |

|

Бит 4 (BP2) |

Смотрите таблицу 8 |

|

Биты 5-6 – «0», когда устройство не находится во внутреннем цикле записи. |

|

|

Бит 7 (WREN) |

Смотрите таблицу 9 |

|

Биты 0-7 – «1» в течение внутреннего цикла записи. |

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.