1. Назовите основные функциональные узлы ЦАП.

2. Каким образом реализуются источники опорного напряжения в ЦАП?

3. Приведите классификацию АЦП по методам формирования выходного сигнала.

4. Как связана разрешающая способность АЦП с диапазоном изменения входного сигнала, количеством разрядов в выходном коде?

5. Как определяется динамическая погрешность АЦП?

6. Чем определяется быстродействие устройства выборки-хранения?

7. Статические и динамические погрешности коммутации. Методы их уменьшения.

8. Что представляет собой переходная характеристика компаратора?

9. Назовите основные функциональные узлы таймера.

10. Какие варианты конструкторско-технологического исполнения АЦП и ЦАП Вам известны?

5. ЗАДАНИЕ НА КОНТРОЛЬНУЮ РАБОТУ

Основное назначение контрольной работы состоит в выработке у студентов умения применять полученные теоретические знания для решения практических задач.

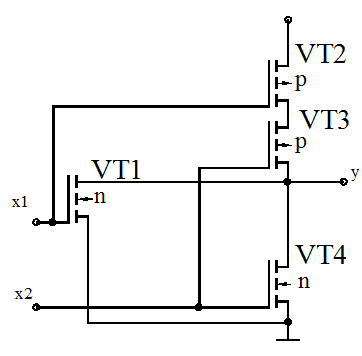

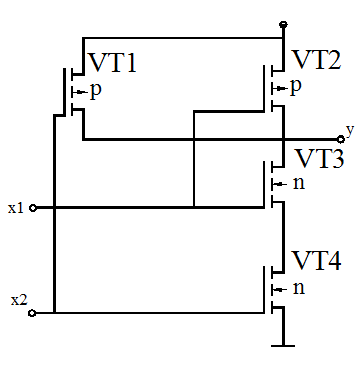

В контрольной работе необходимо определить статические и динамические параметры базовых логических элементов ИЛИ-НЕ (рис.1) и И-НЕ (рис.2) на КМДП транзисторах.

Рис.1 Рис.2

Исходные данные для расчета приведены в табл. 1 и 2.

|

Параметры |

Предпоследняя цифра шифра |

|||||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

0 |

|

|

Тип схемы |

и-не |

или-не |

и-не |

или-не |

и-не |

или-не |

и-не |

или-не |

и-не |

или-не |

|

Частота входного сигнала f, МГц |

10 |

25 |

20 |

15 |

30 |

5 |

10 |

20 |

25 |

15 |

|

Емкость нагрузки |

12 |

5 |

10 |

15 |

3 |

20 |

11 |

8 |

6 |

12 |

|

Параметры |

Последняя цифра шифра |

|||||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

0 |

|

|

Напряжение питания

|

5 |

9 |

5 |

6 |

9 |

5 |

6 |

9 |

5 |

6 |

|

Напряжение

порога переключения транзистора n -типа |

1,5 |

2,6 |

1,6 |

1,8 |

2,8 |

1,7 |

1,5 |

2,4 |

1,6 |

2,0 |

|

Напряжение порога

переключения транзистора p-типа |

-1,5 |

-1,9 |

-1,7 |

-1,5 |

-1,8 |

-1,6 |

-1,7 |

-2,0 |

-1,5 |

-1,9 |

|

Удельная

крутизна транзистора n-типа |

0,33 |

0,9 |

0,45 |

0,5 |

1,1 |

0,2 |

0,85 |

1,3 |

0,6 |

0,35 |

|

Удельная

крутизна транзистора p-типа |

0,3 |

0,8 |

0,4 |

0,45 |

1,0 |

0,2 |

0,7 |

1,1 |

0,55 |

0,3 |

6. МЕТОДИЧЕСКИЕ УКАЗАНИЯ К ВЫПОЛНЕНИЮ КОНТРОЛЬНОЙ РАБОТЫ

6.1. РАСЧЕТ СТАТИЧЕСКИХ ПАРАМЕТРОВ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

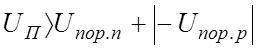

6.1.1. Проверяется условие, обеспечивающее нормальную работу схемы,

,

,

где ![]() -

напряжение питания логического элемента;

-

напряжение питания логического элемента; ![]() -

напряжение порога переключения для транзистора с каналом n-типа;

-

напряжение порога переключения для транзистора с каналом n-типа; ![]() - напряжение порога переключения

для транзистора с каналом р-типа.

- напряжение порога переключения

для транзистора с каналом р-типа.

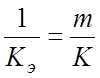

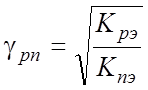

6.1.2. Определяется эквивалентная удельная крутизна транзисторов, входящих в состав логических элементов И-НЕ, ИЛИ-НЕ.

Последовательно и параллельно включенные однотипные

транзисторы, входящие в состав интегральных схем, реализующих логические

элементы И-НЕ, ИЛИ-НЕ, в проводящем состоянии можно заменить одним

эквивалентным транзистором с удельной крутизной ![]() .

.

В случае последовательного включения транзисторов эквивалентная удельная крутизна определяется из соотношения

,

,

где m- число последовательно включенных транзисторов в логической матрице; К-удельная крутизна транзистора.

В случае параллельного включения транзисторов эквивалентная удельная крутизна определяется из соотношения

![]() ,

,

где q- число параллельно включенных транзисторов в логической матрице.

6.1.3.

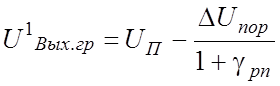

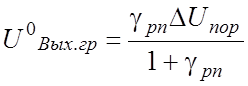

Определяются граничные значения выходного напряжения логической единицы  и выходного напряжения логического

нуля

и выходного напряжения логического

нуля ![]()

![]()

;

;  ,

,

где  ;

;

;

; ![]() и

и

![]() - эквивалентная удельная крутизна

транзисторов p-типа и n-типа соответственно.

- эквивалентная удельная крутизна

транзисторов p-типа и n-типа соответственно.

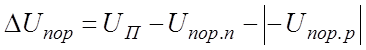

6.1.4. Определяется запас помехоустойчивости логических элементов

![]() ;

; ![]() ,

,

где ![]() -

напряжение логической единицы,

-

напряжение логической единицы, ![]() - напряжение

логического нуля.

- напряжение

логического нуля.

Для

логических элементов на КМДП транзисторах следует принять ![]() и

и ![]() .

.

6.1.5. Определяется ширина переходной области переключательной характеристики логического элемента

![]()

6.2. РАСЧЕТ ДИНАМИЧЕСКИХ ПАРАМЕТРОВ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

6.2.1. Определяется суммарная выходная емкость элемента

![]() ,

,

где ![]() пФ

- емкость затвора-истока транзистора n-типа;

пФ

- емкость затвора-истока транзистора n-типа; ![]() пФ - емкость затвора-истока

транзистора p-типа;

пФ - емкость затвора-истока

транзистора p-типа; ![]() пФ - паразитная

емкость межэлементных соединений;

пФ - паразитная

емкость межэлементных соединений; ![]() - емкость

нагрузки.

- емкость

нагрузки.

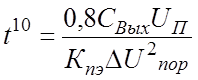

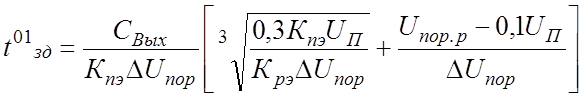

6.2.2. Определяется время включения инвертора

.

.

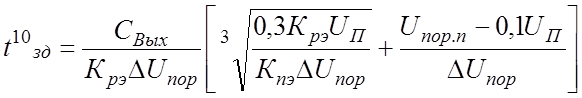

6.2.3. Определяется время задержки включения инвертора

.

.

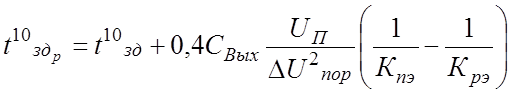

6.2.4. Определяется время задержки распространения сигнала при включении

.

.

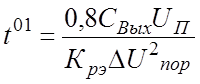

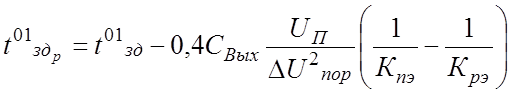

6.2.5. Определяется время выключения инвертора

.

.

6.2.6. Определяется время задержки выключения инвертора

.

.

6.2.7. Определяется время задержки распространения сигнала при выключении

.

.

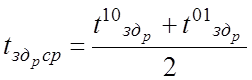

6.2.8. Определяется среднее время задержки распространения сигнала

.

.

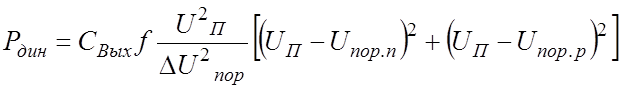

6.2.9. Определяется мощность, потребляемая логическим элементом в динамическом режиме

,

,

где f- частота входного сигнала.

СОДЕРЖАНИЕ

1. Цели и задачи изучения дисциплины………………………………….3

2. Содержание учебной дисциплины……………………………………..4

3. Библиографический список…………………………………………….9

4. Вопросы для самопроверки……………………………………………10

5. Задание на контрольную работу………………………………………13

6. Методические указания к выполнению контрольной работы………14

Редактор Т.В.Шабанова

Сводный темплан 2005 г.

Лицензия ЛР № 020308 от 14.02.97

Санитарно-эпидемиологическое заключение № 78.01.07.953.П.005641.11.03

от 21.11.2003 г.

Подписано в печать Формат 60х84 1/16

Б. кн.-журн. П.л. 1,25 Б.л. 0,625 Изд-во СЗТУ.

Тираж 75 Заказ

Северо-Западный государственный заочный технический университет

Издательство СЗТУ, член Издательско-полиграфической ассоциации

университетов России

191186, Санкт-Петербург, ул. Миллионная, д.5

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.