Цель работы: изучение структуры мультиплексоров и методов синтеза на их основе логических схем.

1. МЕТОДИЧЕСКИЕ УКАЗАНИЯ

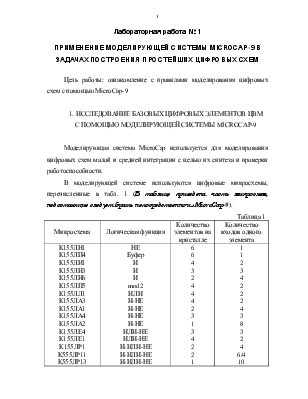

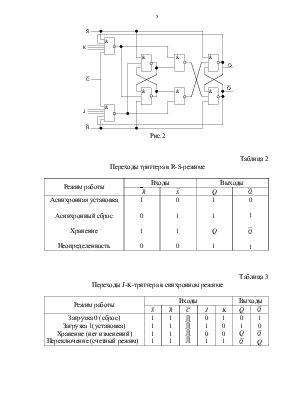

Мультиплексор - это функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких входов данных к выходу. Номер выбранного входа соответствует коду, поданному на адресные входы мультиплексора. Условное изображение мультиплексора показано на рис.1. Мультиплексор имеет N адресных входов А1, А2, ..., АN, М информационных входов D1, D2, ..., DM и вход ОЕ для управления выводом информации (разрешение вывода); при ОЕ=0 мультиплексор работает как обычно, при ОЕ=1 выход узла находится в неактивном состоянии, мультиплексор заперт.

|

|

|

Рис.1 |

Работа мультиплексора может быть описана следующим выражением:

|

|

(1) |

В настоящее время выпускаются промышленностью и получили наибольшее применение мультиплексоры с 4, 8, и 16 информационными каналами.

Одним из применений мультиплексоров является реализация на них логических функций. Как следует из выражения (1), на мультиплексоре с N адресными входами легко может быть реализована переключательная функция N аргументов. Для этого на адресные входы мультиплексора подключается N переменных, а на входы данных подаются константы 1 и 0 в зависимости от конкретного значения переключательной функции на каждом из 2N наборов аргументов.

Другим способом реализации логических схем на мультиплексорах является способ с использованием разложения переключательной функции по составляющим ее переменным.

Рассмотрим функцию 4 переменных F(X1, X2, X3, X4). Обозначим Х4 через L и разложим функцию по переменным Х1, Х2, Х3:

|

|

(2) |

Каждая составляющая правой части этого выражения в зависимости от значений функции на наборах, являющихся соседними по переменной Х4, может принимать значения, приведенные в табл.1.

Таблица 1

|

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

|

|

0 |

L |

L |

1 |

В нижней строке таблицы приведены значения, которые должны быть поданы на информационный вход мультиплексора, определяемый комбинацией соответствующих управляющих сигналов.

Следовательно, на каждый

информационный вход мультиплексора, определяемый комбинацией сигналов на

адресных входах, необходимо подключить сигналы из множества ![]() в соответствии с таблицей истинности

реализуемой переключательной функции. Это свидетельствует о возможности

реализации на мультиплексоре с N адресными входами переключательной функции N+1

аргументов.

в соответствии с таблицей истинности

реализуемой переключательной функции. Это свидетельствует о возможности

реализации на мультиплексоре с N адресными входами переключательной функции N+1

аргументов.

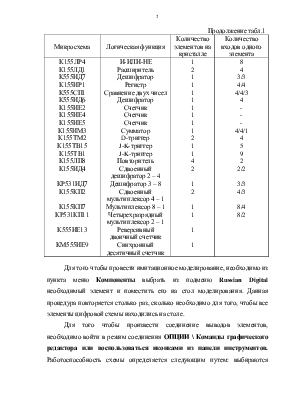

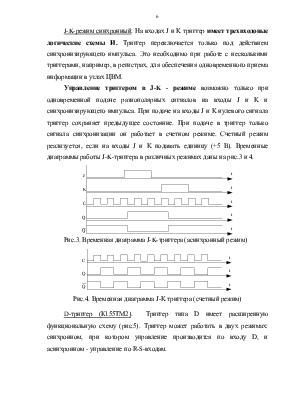

В качестве примера рассмотрим реализацию на мультиплексоре с 3 адресными входами переключательной функции, заданной таблицей истинности (табл.2).

Таблица 2

|

X1 |

X2 |

X3 |

X4 |

F |

Информационные входы |

|

|

0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 |

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 |

0 0 1 0 0 1 1 1 1 1 0 1 1 0 0 0 |

|

|

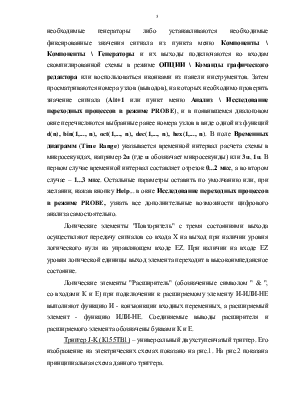

Правый столбец табл.2 заполнен в соответствии с выражением (2) и табл.1, определяющими порядок подключения входов данных мультиплексора для реализации заданной переключательной функции. Функциональная схема включения мультиплексора для реализации рассмотренного примера приведена на рис. 2.

|

|

|

Рис.2 |

2. ОПИСАНИЕ ВЫПОЛНЕНИЯ РАБОТЫ

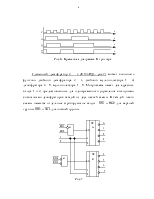

Для выполнения данной работы выбираются 2 мультиплексора для случаев 4-х и 3-х управляющих входов.

3. ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Выполнение работы состоит в проверке работоспособности мультиплексора на 8 и 16 информационных входов, синтезированных в соответствии с индивидуальным заданием, а также схемы, синтезированной по таблице истинности

На входы мультиплексора информация подается в парафазном коде с генератора импульсов. Контроль работоспособности схем осуществляется по таблице истинности функции от четырех переменных.

4. ЗАДАНИЕ К ЛАБОРАТОРНОЙ РАБОТЕ

Для составления таблицы истинности в соответствии с вариантом задания необходимо:

1. Определить число DIG по формуле DIG = 7NV2 + 200 NV + 30, где NV - номер варианта индивидуального задания.

2. Перевести число DIG из десятичной в двоичную систему счисления.

3. Полученное число дополнить до 16 бит, заполняя старшие разряды числа нулями.

4. Составить таблицу истинности четырех переменных. Значение функции на шестнадцатом наборе аргументов определяется 1-м разрядом числа DIG(F(1)=DIG(1)). Нумерация разрядов числа DIG увеличивается в сторону старших разрядов.

5. Реализовать логическую функцию, представленную заданной таблицей истинности, с использованием следующих устройств цифровой техники:

- мультиплексор на 8 каналов К155КП7;

- сдвоенный мультиплексор 4 à 1 К155КП2 (предполагается использование

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.