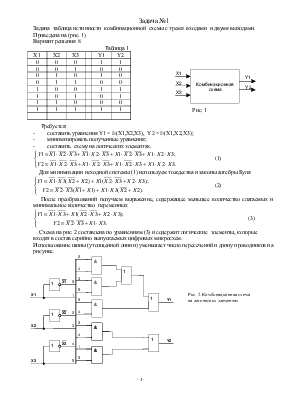

Задана таблица истинности комбинационной схемы с тремя входами и двумя выходами.

Приведена на (рис. 1)

Вариант решения 8

Х1 |

Х2 |

Х3 |

Y1 |

Y2 |

|

|

0 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

1 |

0 |

0 |

|

|

0 |

1 |

0 |

1 |

0 |

|

|

0 |

1 |

1 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

|

|

1 |

1 |

1 |

1 |

1 |

|

|

- составить уравнения Y1 = f1(Х1,Х2,Х3), Y2 = f2(Х1,Х2,Х3);

- минимизировать полученные уравнения;

- составить схему на логических элементах.

(1)

(1)

Для минимизации исходной системы (1) используем тождества и законы алгебры Буля

(2)

(2)

После преобразований получаем выражение, содержащее меньшее количество слагаемых и минимальное количество переменных

(3)

(3)

Схема на рис. 2 составлена по уравнениям (3) и содержит логические элементы, которые входят в состав серийно выпускаемых цифровых микросхем.

Использование шины (утолщенной линии) уменьшает число пересечений и длину проводников на рисунке.

|

Вариант 8.8 отсюда следует что значение 105

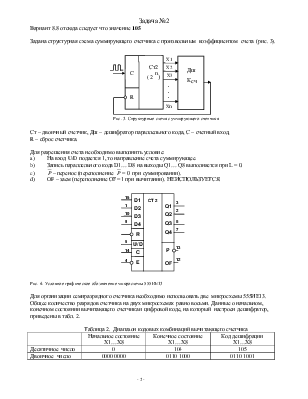

Задана структурная схема суммирующего счетчика с произвольным коэффициентом счета (рис. 3).

Для разрешения счета необходимо выполнить условие:

a) На вход U/D подается 1, то направление счета суммирующее.

b) Запись параллельного кода D1… D8 на выходы Q1… Q8 выполняется при L = 0.

c) ![]() – перенос (переполнение

– перенос (переполнение ![]() =

0 при суммировании).

=

0 при суммировании).

d) OF – заем (переполнение OF= 1 при вычитании). НЕИСПОЛЬЗУЕТСЯ.

Рис. 4. Условное графическое обозначение микросхемы 555ИЕ13

Для организации семиразрядного счетчика необходимо использовать две микросхемы 555ИЕ13.

Общее количество разрядов счетчика на двух микросхемах равно восьми. Данные о начальном, конечном состоянии вычитающего счетчика и цифровой коде, на который настроен дешифратор, приведены в табл. 2.

Таблица 2. Диапазон кодовых комбинаций вычитающего счетчика

|

Начальное состояние Х1…Х8 |

Конечное состояние Х1…Х8 |

Код дешифрации Х1…Х8 |

|

|

Десятичное число |

0 |

104 |

105 |

|

Двоичное число |

0000 0000 |

0110 1000 |

0110 1001 |

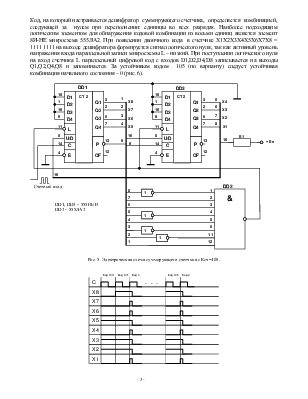

Код, на который настраивается дешифратор суммирующего счетчика, определяется комбинацией, следующей за нулем при переполнении: единицы во всех разрядах. Наиболее подходящим логическим элементом для обнаружения кодовой комбинации из восьми единиц является элемент 8И-НЕ микросхема 555ЛА2. При появлении двоичного кода в счетчике Х1Х2Х3Х4Х5Х6Х7Х8 = 1111 1111 на выходе дешифратора формируется сигнал логического нуля, так как активный уровень напряжения входа параллельной записи микросхемы L – низкий. При поступлении логического нуля на вход счетчика L параллельный цифровой код с входов D1,D2,D4,D8 записывается на выходы Q1,Q2,Q4,Q8 и запоминается. За устойчивым кодом 105 (по варианту) следует устойчивая комбинация начального состояния – 0 (рис. 6).

|

|

Рис. 5. Электрическая схема суммирующего счетчика с Ксч=105.

|

Рис 6. Временная диаграмма схемы.

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

1. Прянишников В.А. Электроника: курс лекций. –СПб.: Корона принт, 1998.

2. Угрюмов Е.П. Цифровая схемотехника. –СПб.: БХВ-Петербург, 2001.

3. Лачин В.И. , Савелов Н.С. Электроника: учебное пособие.- Р н/Д, Феникс, 2000.

4. Партала О.Н. Цифровая электроника. Изд. 2-ое. – СПб.: Наука и техника, 2001.

5. Олифер В.Г., Олифер Н.А. Компьютерные сети. : Питер, 2000.

6. Браммер Ю.А. Импульсная техника. -М.: Высш. шк., 1985.

7. Галичский К.В. Компьютерные системы в телефонии. – СПб.: БХВ-Петербург, 2002.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.