Задача 1

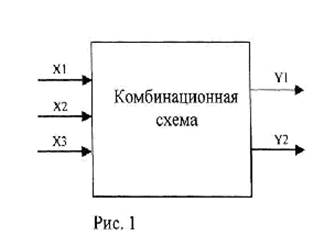

Задана таблица истинности комбинационной схемы с тремя входами и двумя выходами (рис. 1)

Табл. 1

|

X1 |

X2 |

X3 |

Y1 |

Y2 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Требуется:

- составить уравнения Yl = f1, (Xl,X2,X3), Y2 = f2 (Xl,X2,X3);

- минимизировать полученные уравнения;

- составить схему на логических элементах.

Для составления исходных уравнений по данным табл. 1 с помощью совершенной дизъюнктивной формы Количество слагаемых для выходного сигнала Yl равно четырем, для Y2 - четырем. Минтермы единиц для сигнала Yl определены по первой, третьей, пятой и восьмой строкам таблицы. Для Y2 по первой, пятой, шестой и восьмой строкам таблицы.

Запишем выражения системы:

(1)

(1)

Для минимизации исходной системы (1) используем тождества и законы алгебры Буля

(2)

(2)

После преобразований получаем выражение, содержащее меньшее количество слагаемых и минимальное количество переменных

(3)

(3)

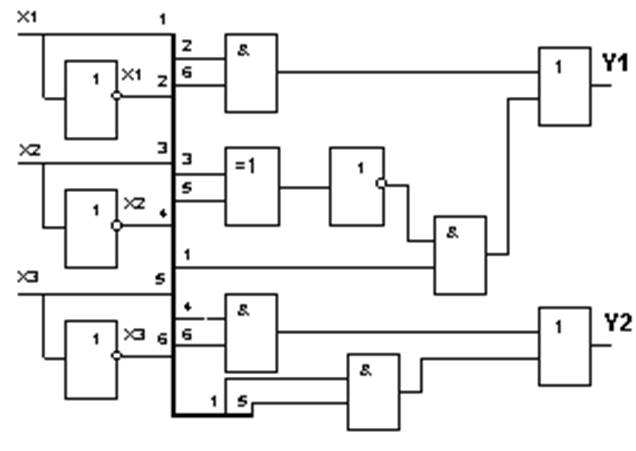

Схема на рис. 2 составлена по уравнениям (3) и содержит логические элементы, которые входят в состав серийно выпускаемых цифровых микросхем. Использование шины (утолщенной линии) уменьшает число пересечений и длину проводников на рисунке.

Рис. 2

Задача 2

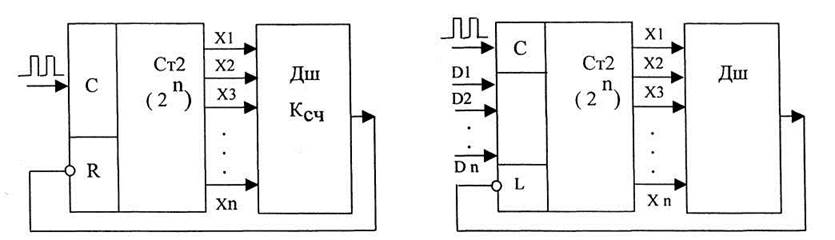

Задана структурная схема суммирующего и вычитающего счетчика с произвольным коэффициентом счета (рис. 3).

а) б)

Ст - двоичный счетчик, Дш - дешифратор параллельного кода, C - счетный вход, R - сброс счетчика, L - вход записи параллельного кода Dl.. .Dn.

Рис. 3. Структурные схемы счетчиков: суммирующего (а), вычитающего (б)

Требуется:

- составить электрическую схему счетчиков;

- пояснить принцип работы схемы с помощью временных диаграмм;

составить таблицу начального и конечного состояний счетчиков, а также кодовой комбинации, на которую настроен дешифратор

Для реализации суммирующего счетчика с коэффициентом Ксч=83 берется двоичный счетчик с коэффициентом большим заданного. Ближайшее число 2n – 27=128

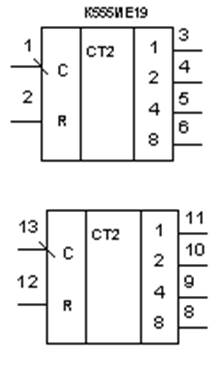

Выбираем микросхему К555ИЕ19 – два четырехразрядных двоичных счетчика, графическую схему которой можно увидеть на рис. 4

R – для установки триггеров счетчика в 0 при подаче на вход R лог.1

С – для подачи счетных импульсов.

Для организации семиразрядного счетчика потребуется одна микросхема КТ555ИЕ19.

Данные о начальном, конечном состоянии счетчика и о цифровом коде, на который настроен дешифратор, приведены в таблице 2.

Рис. 4

Рис. 4

Таблица 2

|

Начальное сост. |

Конечное сост. |

Код дешифратора |

|

|

Десятичное число |

0 |

82 |

83 |

|

Двоичное число |

0000 0000 |

0101 0010 |

0101 0011 |

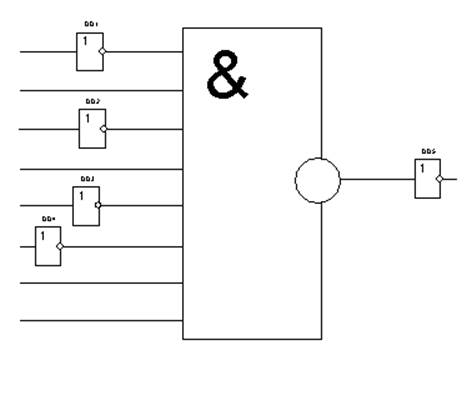

Наиболее подходящим элементом для обнаружения кодовой комбинации, является элемент 8 и-не, соответствующая микросхема КА555ЛА2.

Для дешифратора комбинации 83 подходит микросхема К555ЛН1.

На рис. 5 изображен дешифратор для коэффициента Ксч=83

Для запуска второго счетчика берется микросхема К555ЛИ6 соединенного с выходами первого счетчика.

Рис. 5

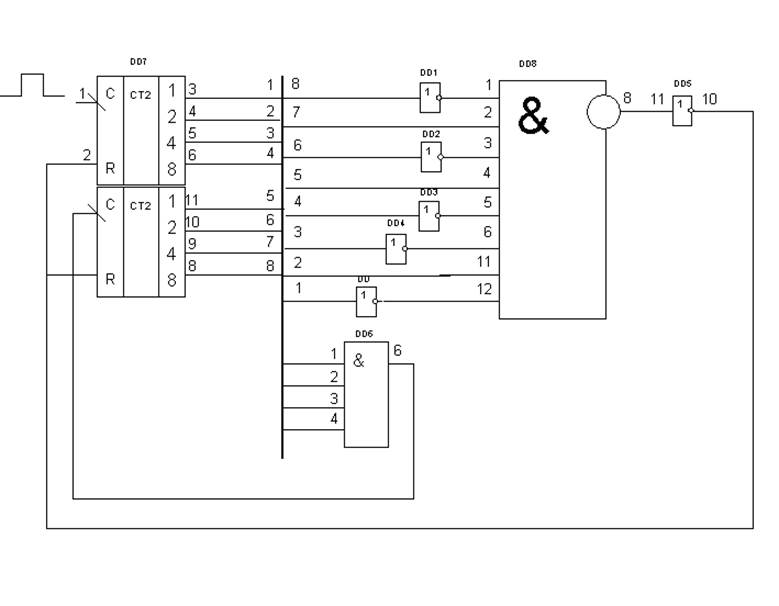

На Рис. 6 изображена схема суммирующего счетчика с коэффициентом Ксч=83.

Рис. 6

DD1-DD5 – К555ЛН1

DD6 – К555ЛИ2

DD7 – К555ИЕ19

DD8 – К555ЛА2

На рис. 7 изображена временная диаграмма работы суммирующего счетчика с Ксч=83

Рис. 7

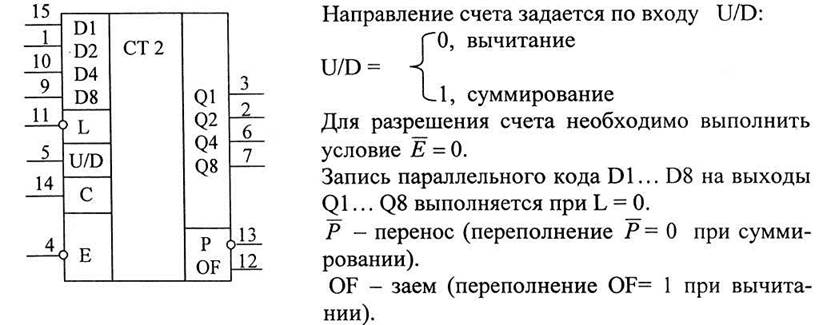

Для реализации схемы вычитающего счетчика с коэффициентом Ксч=83, выбирается двоичный счетчик с коэффициентом счета, большим заданного числа 83. Ближайшее целое число 27 = 128, следовательно, минимальное количество двоичных разрядов равно семи. Микросхемы серийно выпускаемых счетчиков обычно содержат количество разрядов, кратное четырем. Выбираем микросхему 555ИЕ13 (рис. 8) -четырехразрядный реверсивный счетчик, который обеспечивает счет в обоих направлениях и имеет входы установки начального кода

Рис. 8. Условное графическое обозначение микросхемы 555ИЕ13

Для организации семиразрядного счетчика необходимо использовать две микросхемы 555ИЕ13. Общее количество разрядов счетчика на двух микросхемах равно восьми. Данные о начальном, конечном состоянии вычитающего счетчика и цифровой коде, на который настроен дешифратор, приведены втабл.3.

Таблица 3. Диапазон кодовых комбинаций вычитающего счетчика

|

Начальное состояние Xl...Х8 |

Конечное состояние Xl...Х8 |

Код дешифрации Xl...Х8 |

|

|

Десятичное число |

82 |

0 |

255 |

|

Двоичное число |

0101 0010 |

0000 0000 |

1111 1111 |

На рис. 9 представлена электрическая схема

вычитающего счетчика с Ксч=83

На рис. 9 представлена электрическая схема

вычитающего счетчика с Ксч=83

DD1,DD2 – К555ИЕ13

DD3 – К555ЛА2

|

Рис. 10

На рис. 10 представлена временная диаграмм поясняющая принцип работы вычитающего счетчика.

Федеральное агентство по образованию

Государственное образовательное учреждение высшего профессионального образования

(ДВПИ им. В.В.Куйбышева)

Вычислительная техника и информационные технологии

Выполнила студентка

Спец-ть «Радиосвязь, радиовещание и телевидение»

Москвичева Елизавета Сергеевна.

Гр. Зр-2011

Шифр:315128

Проверил преподаватель:.

Владивосток

2006

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.