Министерство образования РФ

Рязанская Государственная Радиотехническая Академия

Кафедра САПР ВС

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

К курсовой работе

по курсу:

«Электротехника и электроника»

на тему:

«Проектирование цифровых устройств с помощью языка VHDL»

Выполнил: _________

студент гр. 047

Проверил: _________

Рязань, 2003

Рязанская государственная радиотехническая академия

Кафедра: САПР ВС

Задание на курсовую работу по дисциплине «Электротехника и электроника»

студенту у А.А. гр. 047

Тема: Проектирование цифровых устройств с помощью языка VHDL

Срок представления работы к защите 15 декабря

Литература.

1. С. Бирюков, Е. Краснов Свето-информационное табло. – Радио, 1987, № 6, с. 17-20.

2. С.В. Триполитов, А.В. Ермилов Микросхемы, диоды, транзисторы: Справочник. – М.: Машиностроение, 1994. – с.ил.

3. С.А. Бирюков Цифровые устройства на МОП – интегральных микросхемах. – М.: Радио и связь, 1990. – 128 с.

Руководитель работы: _________________

( подпись)

Задание выдано: 22.09.2003 г.

Задание принято к исполнению _________________

( подпись)

Задание на курсовую работу…………………………………….2

ВВЕДЕНИЕ……………………………………………………….…4

1.Описание работы схемы………………….……………………5

2.Описание компонентов схемы………………………………...6

ЗАКЛЮЧЕНИЕ…………………………………………………….12

Библиографический список……………………………………..13

ПРИЛОЖЕНИЕ

Исходные тексты компонентов схемы………………………...14

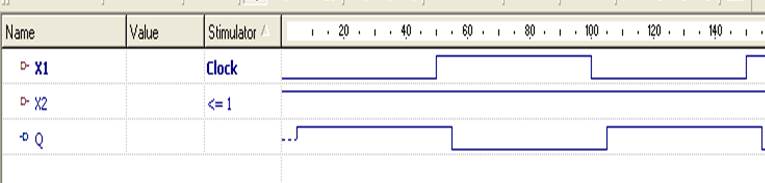

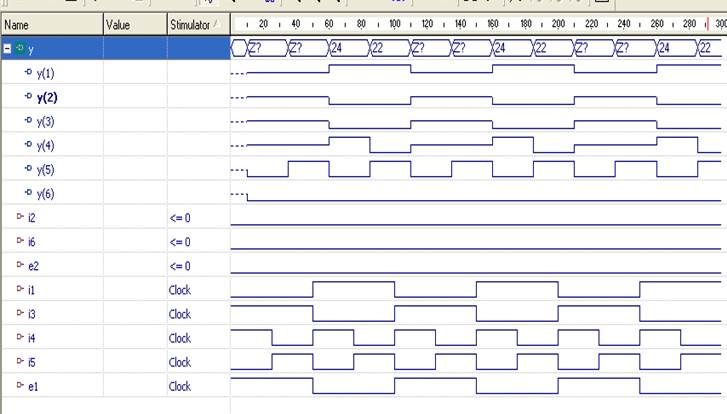

Результаты моделирования…………………………………….19

Широкое внедрение цифровой техники в радиолюбительское творчество связано с появлением интегральных микросхем. Цифровые устройства, собранные на дискретных транзисторах и диодах, имели значительные габаритные размеры и массу; ненадежно работали из-за большого количества элементов, и особенно паяных соединений. Интегральные микросхемы, содержащие в своем составе десятки, сотни, тысячи, а иногда десятки и сотни тысяч компонентов, позволили по-новому подойти к проектированию и изготовлению цифровых устройств. Надежность отдельной микросхемы мало зависит от количества элементов и близка к надежности одиночного транзистора, а потребляемая мощность в пересчете на отдельный компонент резко уменьшается по мере повышения степени интеграции.

В результате на интегральных микросхемах стало возможным собирать сложнейшие устройства, изготовить которые в радиолюбительских условиях без использования микросхем было бы совершенно невозможно.

Широкое распространение получили микросхемы серии К155, однако они потребляют довольно большую мощность. Во многих случаях их можно заменить микросхемами КМОП-структуры, практически не потребляющими мощности в статическом режиме. Разработке цифровых устройств радиолюбителями на микросхемах структуры МОП и КМОП мешает отсутствие систематического изложения вопросов их практического использования в радиолюбительской литературе.

1. ОПИСАНИЕ РАБОТЫ СХЕМЫ

В данной курсовой работе мы будем проектировать узел специализированного устройства системного ПЗУ (СПЗУ). Электрическая схема узла СПЗУ представлена на рис.1.

Полный объём программ, размещенных в системном ПЗУ, равен 4К слов (20 000 байт). Для того чтобы сохранить в разумных пределах длину области, занятой устройством в адресном пространстве ЭВМ, программа разбита на четыре секции, поочередно отображаемые в зону адресов (в окно) ПЗУ. Номер секции, «видимой» в данный момент на общей шине в окне ПЗУ, определяется состоянием регистра коммутации. Он, постоянно доступный на общей шине ЭВМ, позволяет прграммно управлять работой устройства. Наиболее важная функция регистра – переключение секций ПЗУ. Регистр коммутации реализован элементом К580ИР82. Начальный адрес области ПЗУ анализируется предварительным дешифратором. Окончательная дешифрация адресов осуществляется элементом , который управляет доступом к структурам устройства с учетом текущего состояния регистра коммутации. Собственно ПЗУ представлено микросхемой К573РФ2. Зона ПЗУ – адресное пространство, в котором работает программа описываемого устройства. Системная ОЗУ выполнено на микросхеме К541РУ2 с организацией 1К x 4 бит.

При разработке или модификации программ СПЗУ необходимо учитывать специфику устройства: поочередное отображение четырех секций прграммы в одно адресное окно. В условиях столь необычной аппаратуры необходимы специальные меры для выполнения самых распространенных действий: обращение к переменным в области адресов системного ОЗУ и вызова программ из области адресов ПЗУ.

Применение его в стационарных вычислительных комплексах повышает производительность труда; особенно эффективно использование в микроЭВМ, встраиваемых в системы управления.

Приведём словесное описание всех 7 логических элементов нашего узлаа устройства системного ПЗУ .

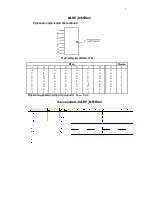

2И-НЕ (К559ИП1П).

Условное графическое обозначение.

|

![]() А

А

![]()

![]()

![]() &Y

&Y

![]() В

В

|

Вход |

Выход Y |

|

|

А |

В |

|

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

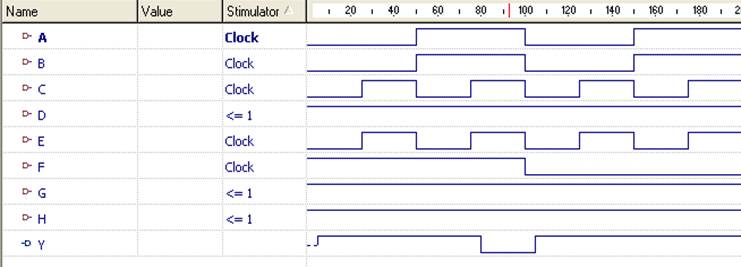

Эпюра работы 2И-НЕ (К559ИП1П).

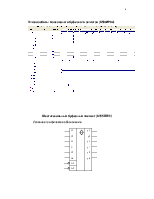

8И-НЕ (К155ЛА2).

Условное графическое обозначение.![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

A

B

C

D

![]()

![]()

![]() Y=ABCDEFGH

Y=ABCDEFGH

![]() E

E

F

G

![]()

![]() H

H

Вход |

Выход |

|||||||

|

A |

B |

C |

D |

E |

F |

G |

H |

Y |

|

0 X X X X X X X 1 |

X 0 X X X X X X 1 |

X X 0 X X X X X 1 |

X X X 0 X X X X 1 |

X X X X 0 X X X 1 |

X X X X X 0 X X 1 |

X X X X X X 0 X 1 |

X X X X X X X 0 1 |

1 1 1 1 1 1 1 1 0 |

Время задержки распространения tзд,р= 5 нс.

Эпюра работы 8И-НЕ (К155ЛА2).

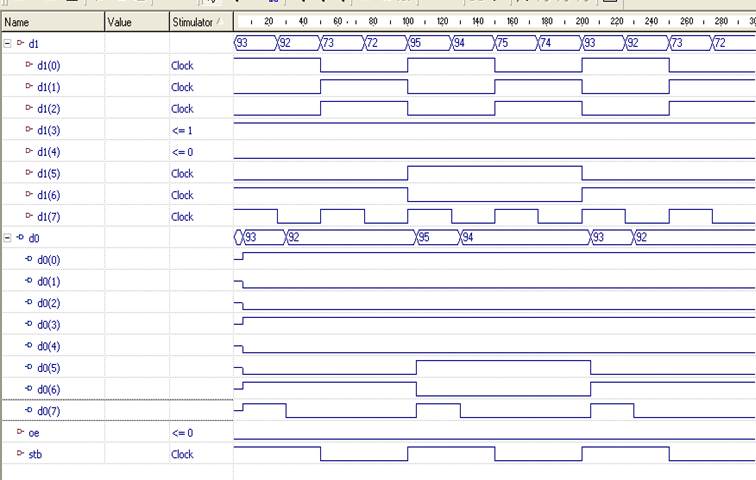

8-разрядный буферный регистр (К580ИР82).

D-регистр «защёлка» с тремя состояниями на выходе. Предназначен для ввода-вывода информациисо стробированием. В зависимости от состояния стробирующего сигнала может работать в режимах шинного формирователя или хранения.

Условное графическое обозначение.

|

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 1 11

1 11

![]() 2 12

2 12

![]() 3 13

3 13

![]() 4

14

4

14

![]() 5 15

5 15

![]() 6 16

6 16

![]() 7 17

7 17

![]() 8 18

8 18

![]()

![]()

![]()

![]()

9

10

![]()

![]() 1…8 – информационные

входы D10…D17; 9 – вход разрешения

выхода OE; 10 –

стробирующий входа STB; 11…18 –

информационные выходы D00…D07.

1…8 – информационные

входы D10…D17; 9 – вход разрешения

выхода OE; 10 –

стробирующий входа STB; 11…18 –

информационные выходы D00…D07.

|

|

Вход STB |

Входы D1 |

Выходы DO |

|

0 0 0 1 |

1 1 0 X |

1 0 X X |

1 0 D00 Z |

D00 – состояние выхода в предыдущем такте; X – логический уровень на входе не влияет на состояние выхода.

Время задержки распространения tзд.р = 5 нс.

Эпюра работы 8-разрядного буферного регистра (К580ИР82).

Шестиканальный буферный элемент (К155ЛП11)

Условное графическое обозначение.

|

|

E1 |

E2 |

I |

y1-y4 |

y5-y6 |

|

0 0 0 0 1 1 |

0 0 1 1 0 0 |

0 1 0 1 0 1 |

0 1 0 1 Z Z |

0 1 Z Z 0 1 |

Время задержки распространения tзд,р= 10 нс

.

Эпюра работы шестиканального буферного элемента (К155ЛП11)

8- разрядный неинвертирующий шинный формирователь (КР580ВА86)

Условное графическое обозначение.

|

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 1

11

1

11

![]() 2

12

2

12

![]() 3 13

3 13

![]() 4 14

4 14

![]() 5 15

5 15

![]() 6 16

6 16

![]() 7 17

7 17

![]() 8 18

8 18

![]()

![]()

![]()

![]() 9

9

10

![]() OE – вход разрешения выхода OE; T- вход направления

передачи

OE – вход разрешения выхода OE; T- вход направления

передачи

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.