Waveform

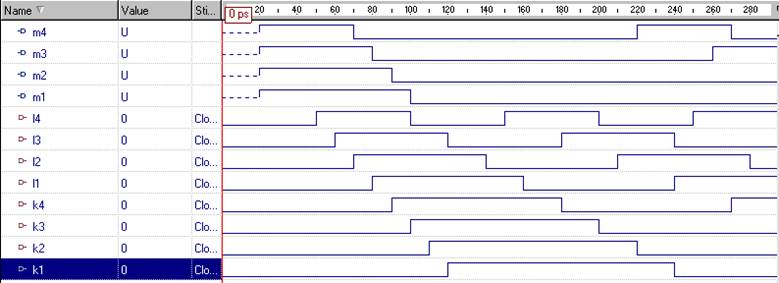

Шинный формирователь с инверсией К589АП26.

Задержка – 50нс

Таблица истинности

|

Логическое состояние по входам логики управления |

Направление передачи информации |

|

|

cs |

bs |

|

|

0 |

0 |

Передача от входов di на выходы db |

|

0 |

1 |

Передача от входов db на выходы do |

|

1 |

1 |

Отсутствие передачи |

|

1 |

0 |

|

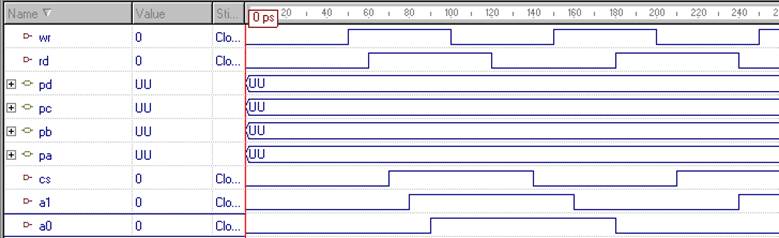

Waveform

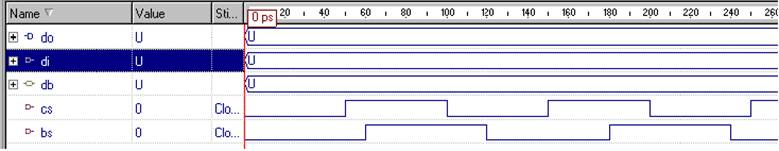

Программируемый параллельный интерфейс КР580ВВ55.

Задержка 20нс

Таблица истинности.

|

Операция |

Сигналы управления |

||||

|

cs |

rd |

wr |

a1 |

a0 |

|

|

Запись в канала A |

0 |

1 |

0 |

0 |

0 |

|

Запись в канала B |

0 |

1 |

0 |

0 |

1 |

|

Запись в канала C |

0 |

1 |

0 |

1 |

0 |

|

Чтение из канала A |

0 |

0 |

1 |

0 |

0 |

|

Чтение из канала B |

0 |

0 |

1 |

0 |

1 |

|

Чтение из канала C |

0 |

0 |

1 |

1 |

0 |

Waveform

Приложение

Код VHDL

D56

library IEEE;

use IEEE.std_logic_1164.all;

entity d56 is

port (

q1: in STD_LOGIC;

q2: in STD_LOGIC;

q3: out STD_LOGIC

);

end d56;

architecture d56 of d56 is

begin

q3<= transport (q1 xor q2) after 20ns;

end d56;

k155la3

library IEEE;

use IEEE.std_logic_1164.all;

entity k155la3 is

port (

f1: in STD_LOGIC;

f2: in STD_LOGIC;

f3: in STD_LOGIC;

f4: in STD_LOGIC;

v1: in STD_LOGIC;

v2: in STD_LOGIC;

v3: in STD_LOGIC;

v4: in STD_LOGIC;

z1: out STD_LOGIC;

z2: out STD_LOGIC;

z3: out STD_LOGIC;

z4: out STD_LOGIC

);

end k155la3;

architecture k155la3 of k155la3 is

begin

z1<=transport not(f1 and v1) after 20ns;

z2<=transport not(f2 and v2) after 20ns;

z3<=transport not(f3 and v3) after 20ns;

z4<=transport not(f4 and v4) after 20ns;

end k155la3;

k155la8

library IEEE;

use IEEE.std_logic_1164.all;

entity k155la8 is

port (

t1: in STD_LOGIC;

t2: in STD_LOGIC;

t3: in STD_LOGIC;

t4: in STD_LOGIC;

e1: in STD_LOGIC;

e2: in STD_LOGIC;

e3: in STD_LOGIC;

e4: in STD_LOGIC;

w1: out STD_LOGIC;

w2: out STD_LOGIC;

w3: out STD_LOGIC;

w4: out STD_LOGIC

);

end k155la8;

architecture k155la8 of k155la8 is

begin

w1<= transport not (t1 and e1) after 20ns;

w2<= transport not (t2 and e2) after 20ns;

w3<= transport not (t3 and e3) after 20ns;

w4<= transport not (t4 and e4) after 20ns;

end k155la8;

k155la2

library IEEE;

use IEEE.std_logic_1164.all;

entity k155la2 is

port (

A: in STD_LOGIC;

B: in STD_LOGIC;

C: in STD_LOGIC;

D: in STD_LOGIC;

E: in STD_LOGIC;

F: in STD_LOGIC;

G: in STD_LOGIC;

H: in STD_LOGIC;

Y: out STD_LOGIC

);

end k155la2;

architecture k155la2 of k155la2 is

begin

Y<= transport not ( A and B and C and D and E and F and G and H ) after 27ns;

end k155la2;

k559ip2p

library IEEE;

use IEEE.std_logic_1164.all;

entity k559ip2p is

port (

k1: in STD_LOGIC;

k2: in STD_LOGIC;

k3: in STD_LOGIC;

k4: in STD_LOGIC;

l1: in STD_LOGIC;

l2: in STD_LOGIC;

l3: in STD_LOGIC;

l4: in STD_LOGIC;

m1: out STD_LOGIC;

m2: out STD_LOGIC;

m3: out STD_LOGIC;

m4: out STD_LOGIC

);

end k559ip2p;

architecture k559ip2p of k559ip2p is

begin

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.