Модель Испытательного стенда

VHDL Испытательный стенд может обеспечивать входы моделирования, а также проверять выходы проекта. Например, Вы можете создавать VHDL программу, которая запишет выходы проекта в текстовой файл и сравнит их со справочным файлом, имеющим предполагаемые величины. Эта методология обеспечивает наиболее полную проверку проекта с минимальным взаимодействием с пользователем.

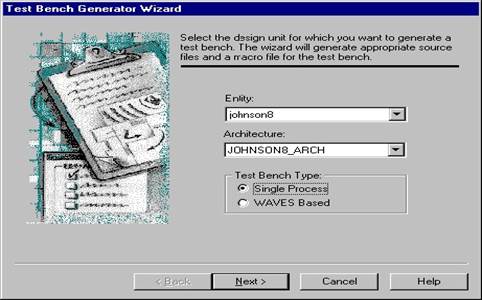

Создание Испытательных стендов - утомительный процесс. Мастер Испытательного стенда автоматизирует этот процесс, руководя Вами все время. Сначала, он спросит, Вас, чтобы Вы выбрали верхний уровень проектирования сущности, которое будет проверено. Затем, Вы должны ввести название файла формы сигнала с требуемыми входами и выходами. После ответа на несколько дополнительных вопросов, Мастер Испытательного стенда накапливает необходимую информацию и создает шаблон для испытательной программы. Вы можете редактировать сгенерированный Мастером файл; добавлять собственные испытательные сценарии и дополнительные входы, если требуется.

Мастер создания испытательного стенда

Пример Begin

— Unit Under Test port map UUT : counter8 port map

( CLK => CLK,

RESET => RESET,

CE => CE,

LOAD => LOAD,

DIR => DIR,

DIN => DIN,

COUNT => COUNT );

end TB_ARCHITECTURE;

configuration TESTBENCH _FOR_counter8 of counter8_tb is for TB_ ARCHITECTURE for UUT : counter8 use entity work.counter8(COUNTER8_ARCH);

end for;

end for;

end TESTBENCH_FOR_counter8;

Мастер Испытательного стенда допускает, чтобы Вы создали шаблон, в соответствии с спецификацией IEEE WAVES 1029.1 Эти СИГНАЛЫ (WAVES ) специфицированы специально для создания файлов испытательного стенда на языке VHDL. Они описывают входы моделирования при помощи определенного языка который реализован как набор VHDL библиотек. Это поддерживает проверку и испытание оборудования проектов на любом уровне абстракции. Вы не должны быть знакомы со спецификацией СИГНАЛА (WAVES), чтобы создать этот файл. Если Вы выбираете эту опцию, то Мастер Испытательного стенда автоматически форматирует вашу программу Испытательного стенда, используя спецификацию СИГНАЛА (WAVES ). Главные выгоды от использования этого формата - способность форматировать вход моделирования и выходные файлы так, чтобы они были переносимы между различными моделирующими устройствами. Формат WAVE также содержит некоторые очень полезные функции высокого уровня для сравнения версий моделирования без того, чтобы писать длинный VHDL код. Стандартные функции Испытательного стенда обеспечиваются в компилируемой библиотеке WAVE и допускают чтение и запись файла испытательного стенда в формате WAVE.

Различия между Испытательным стендом WAVE и другим файлом Испытательного стенда следующие:

формы сигнала, включая выражения формулы и типы стимулов (stimulator)

Испытательный стенд WAVE имеет некоторые очень полезными функциями

Испытательный стенд WAVE обеспечивает стандартный формат файла для данных высокого уровня для типичных действий испытательного стенда обеспечивает стандартный формат файла для данных о форме сигнала, включая формулы и типы стимуляторов.

имеет некоторые очень полезные функции высокого уровня для типичных операций тестовых панелей.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.