in2: in STD_LOGIC;

Res: out STD_LOGIC

);

end k155tl3;

architecture k155tl3 of k155tl3 is

begin

process (in1,in2 )

begin

if in1'event then

Res <= not (in1 and in2) after 12ns ;

end if;

end process;

-- <<enter your statements here>>

end k155tl3;

К155ИД7

--- File: k155id7.vhd

-- created by Design Wizard: 03/19/04 17:23:17

-library IEEE;

use IEEE.std_logic_1164.all,IEEE.std_logic_arith.all;

entity k155id7 is

port (

inf: in STD_LOGIC_VECTOR (2 downto 0);

E1: in STD_LOGIC;

E2: in STD_LOGIC;

E3: in STD_LOGIC;

Res: out STD_LOGIC_VECTOR (7 downto 0)

);

FUNCTION To_Integer( b : STD_LOGIC_VECTOR;size:integer) RETURN integer is

variable i:integer;

variable j:integer;

variable k,d,e,f:integer;

begin

i:=0;

j:=size-1;

L1:loop

if b(j)='1' then

k:=j;

d:=1;

L2:loop

exit L2 when k<=0;

d:=d*2;

k:=k-1;

end loop L2;

i:=i+d;

end if;

exit L1 when j<=0;

j:=j-1;

end loop L1;

return i;

end function To_Integer;

end k155id7;

architecture k155id7 of k155id7 is

begin

process (inf,e1,e2,e3)

variable K:STD_LOGIC_VECTOR (7 downto 0);

variable p:integer;

variable i,j,d,e,f:integer;

begin

if e1='0' and e2='0' and e3='1' then

K:="00000000";

p:=To_Integer(inf,3);

K(p):='1';

else

K:="11111111";

end if;

Res<=K after 19ns;

end process;

-- <<enter your statements here>>

end k155id7;

Top.vhd

library IEEE;

use IEEE.std_logic_1164.all;

entity tip is

port (

bprq: in STd_LOGIC_VECTOR (6 downto 0);

xack: in STd_LOGIC;

on_off1: in STd_LOGIC;

ram_eprom: in STd_LOGIC;

enram:in STd_LOGIC;

adrram: in STd_LOGIC;

adrio: in STd_LOGIC;

ale: in STD_LOGIC;

lock: in STD_LOGIC;

den: in STD_LOGIC;

bclk1:in STD_LOGIC;

ben: out STD_LOGIC;

bprn: out STD_LOGIC_VECTOR (6 downto 0);

rdy2: out STD_LOGIC;

csb: out STD_LOGIC;

busy: out STD_LOGIC;

ale1: out STD_LOGIC

);

end tip;

architecture tip of tip is

component k155ln1 is

port (

in1: in STd_LOGIC;

Res1: out STd_LOGIC

);

end component;

component k155la4 is

port (

in1: in STd_LOGIC;

in2: in STd_LOGIC;

in3: in STd_LOGIC;

Res: out STd_LOGIC

);

end component;

component k155tm2 is

port (

notS: in STd_LOGIC;

notR: in STd_LOGIC;

d: in STd_LOGIC;

C: in STd_LOGIC;

Q: out STd_LOGIC;

notQ: out STd_LOGIC

);

end component;

component k155iv1 is

port (

vh: in STd_LOGIC_VECTOR (7 downto 0);

E : in STd_LOGIC;

ot: out STd_LOGIC_VECTOR (2 downto 0);

G: out STd_LOGIC;

E0:out STd_LOGIC

);

end component;

component k155tl2 is

port (

in1: in STd_LOGIC;

Res: out STd_LOGIC

);

end component;

component k155tl3 is

port (

in1: in STd_LOGIC;

in2: in STd_LOGIC;

Res: out STd_LOGIC

);

end component;

component k155id7 is

port (

inf: in STd_LOGIC_VECTOR (2 downto 0);

E1: in STd_LOGIC;

E2: in STd_LOGIC;

E3: in STd_LOGIC;

Res: out STd_LOGIC_VECTOR (7 downto 0)

);

end component;

signal one,zero:STD_LOGIC;

signal sig1,sig2,sig3,sig21,sig4,sig5,sig6,sig7,sig8,sig9,sig10,sig11,sig12,sig13,sig14,sig15,sig16,sig17,sig18,sig19,sig20:STD_LOGIC;

begin

one<='1';

zero<='0';

d1:k155tl2 port map (in1=>ale,Res=>sig12);

d2:k155tl2 port map (in1=>sig12,Res=>sig11);

d3:k155ln1 port map (in1=>sig11,Res1=>sig10);

ale1<=sig11;

d4:k155ln1 port map (in1=>den,Res1=>sig13);

d5:k155tl3 port map (in1=>sig13,in2=>lock,Res=>sig16);

d6:k155tl3 port map (in1=>sig13,in2=>sig16,Res=>sig14);

sig15<=Den;

d7:k155iv1 port map (vh(0)=>bprq(0),vh(1)=>bprq(1),vh(2)=>bprq(2),vh(3)=>bprq(3),vh(4)=>sig6,vh(5)=>bprq(4),vh(6)=>bprq(5),vh(7)=>bprq(6),

E=>zero, ot(0)=>sig1,ot(1)=>sig2,ot(2)=>sig3,E0=>sig4,G=>sig5);

d8:k155id7 port map (inf(0)=>sig1,inf(1)=>sig2,inf(2)=>sig3,E1=>sig5,E2=>sig4,E3=>sig7,

res(0)=>bprn(0),res(1)=>bprn(1),res(2)=>bprn(2),res(3)=>sig20,res(4)=>bprn(3),res(5)=>bprn(4),res(6)=>bprn(5),res(7)=>bprn(6));

d9:k155la4 port map (in1=>on_off1,in2=>ram_eprom,in3=>enram,Res=>sig8);

d10:k155la4 port map (in1=>sig8,in2=>adrram,in3=>adrio,Res=>sig9);

d11:k155tm2 port map (notS=>xack,notR=>one,C=>sig10,D=>sig9,Q=>sig6);

rdy2<=sig6;

d12:k155tl3 port map (in1=>sig20,in2=>sig19,res=>sig17);

d13:k155tm2 port map (notS=>one,notR=>sig14,D=>sig17,C=>bclk1,Q=>sig18,notQ=>sig19);

ben<=sig19;

d14:k155tl3 port map (in1=>sig18,in2=>sig15,Res=>csb);

d15:k155tl3 port map (in1=>sig19,in2=>sig19,Res=>sig7);

busy<=sig7;

end tip;

Схема устройства.

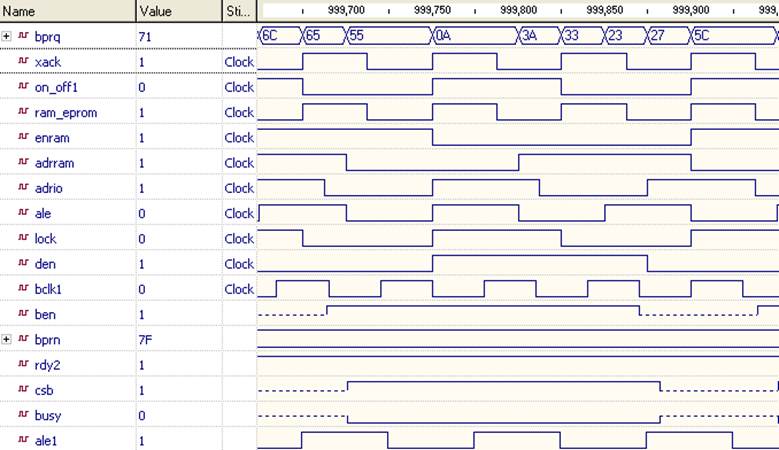

Waveform схемы

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.