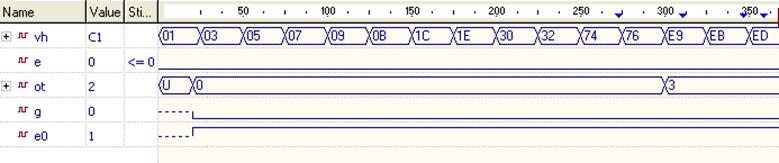

Waveform

Дешифратор – демультиплексор K155ИД7.

DI1,DI2,DI4 – входы адресного кода

E1, E2, E3 – разрешающие входы

D0(0) . . D0(7) - выход

Таблица активизированных выходов ИД7

|

DI4 |

DI2 |

DI1 |

_ E1 |

_ E2 |

E3 |

Выход |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

2 |

|

0 |

1 |

1 |

0 |

0 |

1 |

3 |

|

1 |

0 |

0 |

0 |

0 |

1 |

4 |

|

1 |

0 |

1 |

0 |

0 |

1 |

5 |

|

1 |

1 |

0 |

0 |

0 |

1 |

6 |

|

1 |

1 |

1 |

0 |

0 |

1 |

7 |

|

x |

x |

x |

0 |

x |

x |

На всех выходах ‘1’ |

|

x |

x |

x |

x |

1 |

x |

|

|

x |

x |

x |

x |

x |

0 |

Задержка 19 нс.

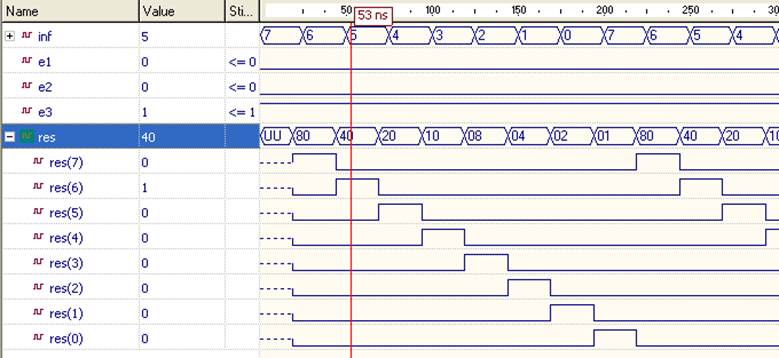

Waveform

Триггеры Шмидта К155ТЛ2, К155ТЛ3.

К155ТЛ2 – шесть триггеров Шмидта с инверсией

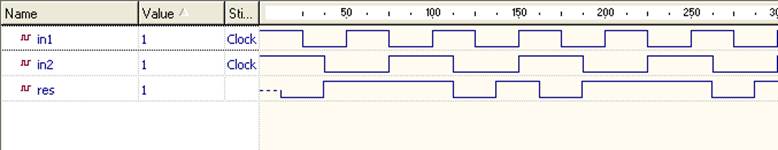

Waveform

K155ТЛ3 – четыре триггера Шмидта с логическими элементами ‘2И-НЕ’ на входе

Waveform

Приложение

Код VHDL

K155ЛН1

--- File: c:\my designs\arbiter\SRC\k155ln1.VHD

-- created by Design Wizard: 03/11/04 10:40:25

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155ln1 is

port (

in1: in STD_LOGIC;

Res1: out STD_LOGIC

);

end k155ln1;

architecture k155ln1 of k155ln1 is

begin

Res1<=not in1 after 22 ns;

-- <<enter your statements here>>

end k155ln1;

К155ЛА4

--- File: c:\my designs\arbiter\SRC\k155la4.VHD

-- created by Design Wizard: 03/11/04 10:40:25

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155la4 is

port (

in1: in STD_LOGIC;

in2: in STD_LOGIC;

in3: in STD_LOGIC;

Res: out STD_LOGIC

);

end k155la4;

architecture k155la4 of k155la4 is

begin

process

begin

wait for 14ns;

Res<=not(in1 and in2 and in3);

end process;

-- <<enter your statements here>>

end k155la4;

К155ТМ2

--- File: k155tm2.vhd

-- created by Design Wizard: 03/11/04 11:48:47

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155tm2 is

port (

notS: in STD_LOGIC;

notR: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

Q: out STD_LOGIC;

notQ: out STD_LOGIC

);

end k155tm2;

architecture k155tm2 of k155tm2 is

begin

process (D,C,notR,notS)

variable F:STD_LOGIC;

begin

if notS='1' and notR='1' and C'event and C='1' then

F:=D;

end if;

if (notS and notR)='0' then

F:=not notS;

end if;

Q<= transport F after 30 ns;

notQ<=transport not F after 30 ns;

end process;

end k155tm2;

К155ИВ1

--- File: k155iv1.vhd

-- created by Design Wizard: 03/19/04 13:45:36

-library IEEE;

use IEEE.std_logic_1164.all,IEEE.STD_LOGIC_ARITH.all;

entity k155iv1 is

port (

vh: in STD_LOGIC_VECTOR (7 downto 0);

E : in STD_LOGIC;

ot: out STD_LOGIC_VECTOR (2 downto 0);

G: out STD_LOGIC;

E0:out STD_LOGIC

);

end k155iv1;

architecture k155iv1 of k155iv1 is

begin

process

variable i:integer;

begin

wait for 20 ns;

if E='1' then

ot<="111";

G<='1';

E0<='1';

end if;

if E='0' then

if vh="11111111" then

ot<="111";

G<='1';

E0<='0';

end if;

if vh="11111110" then

ot<="111";

G<='0';

E0<='1';

end if;

i:=7;

L1:loop

if vh(i)='0' then

ot<=CONV_STD_LOGIC_VECTOR(integer(7-i),3);

G<='0';

E0<='1';

end if;

exit L1 when vh(i)='0' or i=0;

i:=i-1;

end loop L1;

end if;

-- <<enter your statements here>>

end process;

end k155iv1;

К155ТЛ2

--- File: c:\my designs\arbiter\SRC\k155tl2.VHD

-- created by Design Wizard: 03/11/04 10:40:25

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155tl2 is

port (

in1: in STD_LOGIC;

Res: out STD_LOGIC

);

end k155tl2;

architecture k155tl2 of k155tl2 is

begin

process (in1 )

begin

if in1'event then

Res <= not in1 after 12ns ;

end if;

end process;

end k155tl2;

К155ТЛ3

--- File: k155tl3.vhd

-- created by Design Wizard: 03/19/04 17:18:03

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155tl3 is

port (

in1: in STD_LOGIC;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.