Федеральное Агентство по Образованию

РЯЗАНСКАЯ ГОСУДАРСТВЕННАЯ РАДИОТЕХНИЧЕСКАЯ АКАДЕМИЯ

Кафедра САПР ВС

Пояснительная записка

к курсовой работе по курсу "Схемотехника ЭС"

на тему:

“Моделированиецифровых устройств

с использованием пакета VHDL”

Рязань, 2005 г.

СОДЕРЖАНИЕ

1.Моделирование элементов………………………………………………..........4

1.1. Схема КР1533АП6

1) КР1533АП6_1……………………………………………….4

2)КР1533АП6…………………………………………………..5

1.2. Схема КР1533ЛЛ1 (2-ИЛИ)…………………………………………..7

1.3. Схема К561ЛН2………………………………………………………..8

1.4. Схема КР1533АП5 (шинный формирователь)……………………....9

1.5. СхемаКР1533ИР22 (регистр)……………………………………….11

Заключение…………………………………………………………………………...14

Список литературы…………………………………………………………………..15

Приложение 1: Текст программы, моделирующей работу схемы………………..16

Приложение 2: Результаты моделирования схемы ………………………………..18

ВВЕДЕНИЕ

Широкое распространение цифровой техники, ее доступность обывателю и дешевизна обусловлены появлением интегральных микросхем. Цифровые устройства, собранные на базе дискретных транзисторов и диодов, имели значительные габаритные размеры и массу; обладали невысокой надежностью в связи с наличием большого числа элементов и паяных связей между ними. Интегральные микросхемы, содержащие в своем составе десятки и сотни тысяч компонентов, позволили по-новому подойти к проектированию и изготовлению цифровых устройств.

В процессе усовершенствования интегральных технологий стало возможным создание сложнейших устройств, надежных и обладающих малыми габаритами и высоким быстродействием.

Традиционный подход к проектированию дискретных вычислительных систем (ДС) состоит в последовательном решении задач анализа и оптимизации некоторого начального варианта проектируемой ДС. Поэтому давней мечтой разработчиков ДС было создание единых средств описания ДС, которые позволяли бы решать задачи верификации и синтеза схем с различной степенью детальности их описания и, таким образом, объединять этапы проектирования в единый процесс нисходящего проектирования "сверху вниз". Появление языка VHDL в определенной степени позволяет автоматизировать задачи проектирования от описания алгоритма функционирования ДС до реализации кристаллов микросхем. При этом понятие синтез следует определить как формализованный процесс построения схемы из некоторого заданного набора компонентов.

1. МОДЕЛИРОВАНИЕ ЭЛЕМЕНТОВ.

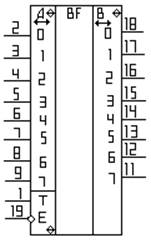

1.1.Схема КР1533АП6.

Микросхема представляет собой восьмиканальный двунаправленный формирователь (приемопередатчик) с тремя состояниями на выходе. Назначение выводов:

1- вход управления информации Т;

2…9 – вход/выход А0...7;

11…18 - вход/выход В7...0;

19 –вход управления третьим состоянием![]() .

.

Таблица истинности

рис.1.Схема электрическая принципиальная КР1533АП6.

|

Входы |

управления |

Операция |

|

Т |

|

|

|

0 |

0 |

В→А |

|

1 |

0 |

А←В |

|

0 |

1 |

◊ |

|

1 |

1 |

◊ |

Примечание: ◊- состояние высокого импеданса.

В общей схеме в наличие имеется три аналогичных элемента (КР1533АП6), но отличие заключается в том, что у первых двух на вход управления информацией Т (см. рис.1) подан высокий уровень – 5В. Таким образом, опишем два первых элемента (kr1533ap6_1), задав входу Т постоянный уровень <1>.

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity kr1533ap6_1 is

port (

A: out STD_LOGIC_VECTOR (7 downto 0);

T: in STD_LOGIC:='1';

E: in STD_LOGIC;

B: in STD_LOGIC_VECTOR (7 downto 0)

);

end kr1533ap6_1;

architecture kr1533ap6_1 of kr1533ap6_1 is

begin

Process (E, B)

variable i: integer;

begin

If E='0' then A<=transport B after 26 ns;

else For i in 0 to 7 loop

A(i)<=transport 'U' after 26 ns;

end loop;

end if;

end process;

endkr1533ap6_1;

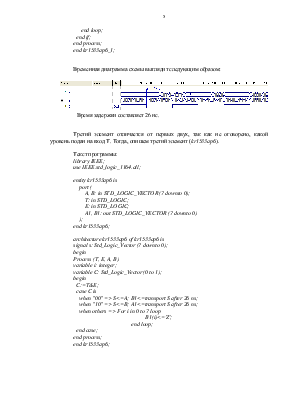

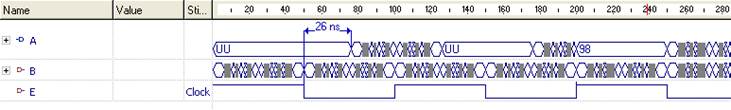

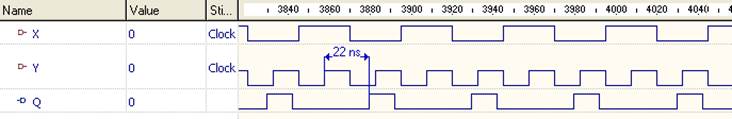

Временная диаграмма схемы выглядит следующим образом:

Время задержки составляет 26 нс.

Третий элемент отличается от первых двух, так как не оговорено, какой уровень подан на вход Т. Тогда, опишем третий элемент (kr1533ap6).

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity kr1533ap6 is

port (

A, B: in STD_LOGIC_VECTOR (7 downto 0);

T: in STD_LOGIC;

E: in STD_LOGIC;

A1, B1: out STD_LOGIC_VECTOR (7 downto 0)

);

end kr1533ap6;

architecture kr1533ap6 of kr1533ap6 is

signal s: Std_Logic_Vector (7 downto 0);

begin

Process (T, E, A, B)

variable i: integer;

variable C: Std_Logic_Vector (0 to 1);

begin

C:=T&E;

case C is

when "00" => S<=A; B1<=transport S after 26 ns;

when "10" => S<=B; A1<=transport S after 26 ns;

when others => For i in 0 to 7 loop

B1(i)<='Z';

end loop;

end case;

end process;

end kr1533ap6;

Временная диаграмма схемы выглядит следующим образом:

Время задержки составляет 26 нс.

1.2.Схема КР1533ЛЛ1 (2-ИЛИ).

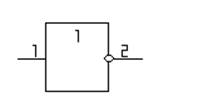

Логический элемент 2-ИЛИ выполняет логическую функцию ИЛИ.

Логическая функция элемента: Q=XVY. В общей схеме имеются два одинаковых элемента (см. рис.2). Опишем один из них.

|

Х |

Y |

Q |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Таблица истинности элемента 2ИЛИ.

Рис.2.Схема электрическая принципиальная КР1533ЛЛ1.

Текст программы:

Время задержки составляет 22 нс.

1.3.Схема логического элемента К561ЛН2.

Логический элемент К561ЛН2 реализует логическую функцию НЕ.

Логическая функция элемента: ![]()

Рис.3. Схема электрическая принципиальная К155ЛН2

|

X |

Y |

|

0 |

1 |

|

1 |

0 |

Таблица истинности элемента НЕ

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity k561ln2 is

port (

X: in STD_LOGIC;

Y: out STD_LOGIC

);

end k561ln2;

architecture k561ln2 of k561ln2 is

begin

Y<=transport not X after 80 ns;

end k561ln2;

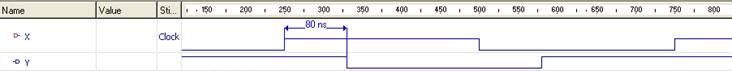

Временная диаграмма работы логического элемента К561ЛН2.

Время задержки составляет 80 нс

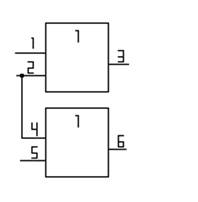

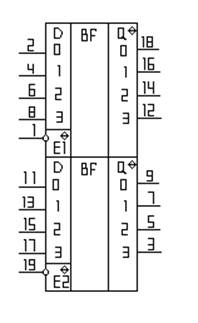

1.4. Схема элемента КР1533АП5.

Микросхема представляет собой два четырехканальных формирователя с тремя состояниями на выходе с инверсным управлением.

Назначение выводов:

1,

19 — входы разрешения снятия состояния высокого импеданса ![]() ;

;

2 — вход информационный первого элемента 0;

3 — выход информ. второго элемента 3; 4 — вход информ. первого элемента 1;

5—выход информ. второго элемента ; 6 — вход информ. первого элемента 2;

7—выход информ. второго элемента 1; 8 — вход информ. первого элемента 3;

9 — выход информ. второго элемента 0; 11 — вход информ. второго элемента 0;

12—выход информ. первого элемента 3; 13 — вход информ. второго элемента 1;

14 — выход информ. первого элемента 2; 15— вход информ. второго элемента 2;

16 — выход информ. первого элемента 1; 17—вход информ. второго элемента 3;

18 — выход информ. первого элемента 0.

Таблица истинности

|

|

Входы |

Выходы |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

Х |

◊ |

Рис.4. Схема электрическая

принципиальная КР1533АП5.

Текст программы:

libraryIEEE;

useIEEE.std_logic_1164.all;

entitykr1533ap5 is

port (

E: in STD_LOGIC;

D: in STD_LOGIC_VECTOR (3 downto 0);

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end kr1533ap5;

architecture kr1533ap5 of kr1533ap5 is

begin

Process (E, D)

variable i: integer;

begin

If e='0' then Q<=transport D after 20 ns;

else

for i in 0 to 3 loop

Q(i)<=transport 'Z' after 32ns;

end loop;

end if;

end process;

end kr1533ap5;

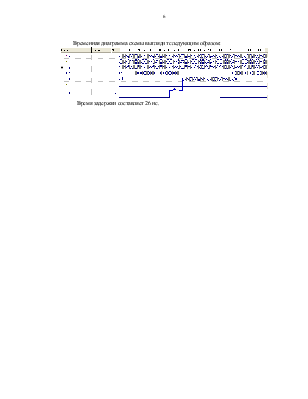

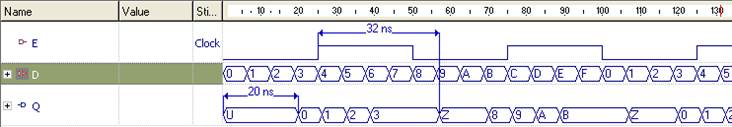

Временная диаграмма работы логического элемента КР1533АП52.

Время задержки при переходе из состояния «выключено» в состояние низкого (высокого) уровня составляет 20 нс, время задержки распространения при переходе из состояния низкого (высокого) уровня в состояние выключено составляет 32 нс.

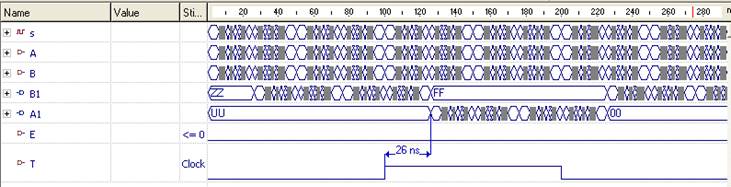

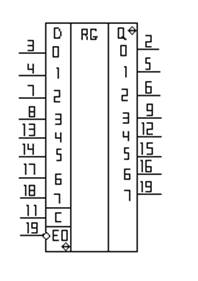

1.5.Схема КР1533ИР22.

Mикросхема представляет собой восьмиразрядный регистр на триггерах с защелкой с тремя состояниями на выходе. Она предназначена для управления большой емкостной или низкоомной нагрузками.

Назначение выводов:

1 — вход разрешения снятия состояния высокого

импеданса ![]() ;

;

2 — выход Q0;

3 — вход информационный DO;

4 —вход информационный D1;

5 — выход Q1;

б —выход Q2;

7 —вход информационный D2;

8 — вход информационный D3;

9 —выход Q3;

11—вход тактовый С;

12—выход Q4;

13—вход информационный D4;

14—вход информационный D5;

15—выход Q5;

16—выход Q6;

17—вход информационный D6;

18—вход информационный D7;

19—выход Q7. Таблица истинности

|

Вход |

Выход |

||

|

|

С |

D |

Q |

|

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

0 |

X |

Q0 |

|

1 |

Х |

X |

Z |

Рис.5. Схема электрическая принципиальная КР1533ИР22.

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity kr1533ir22 is

port (

D: in STD_LOGIC_VECTOR (7 downto 0);

C: in STD_LOGIC;

ED: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (7 downto 0)

);

end kr1533ir22;

architecture kr1533ir22 of kr1533ir22 is

begin

Process (ED, C, D)

variable i: integer;

begin

If ED='1' then

for i in 0 to 7 loop

Q(i)<=transport 'Z' after 19 ns;

end loop;

else

if c='1' then Q<=transport D after 14 ns;

end if;

end if;

end process;

endkr1533ir22;

Временная диаграмма работы логического элемента КР1533ИР

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.