Розділ II

СТРУКТУРИ БАЗОВИХ ЛОГІЧНИХ ЕЛЕМЕНТІВ

2.1. Характеристика цифрових сигналiв

Цифровi сигнали “0’’, “1”, якi використовуються в курсі дискретної математики, є iдеалiзацiєю тих сигналiв, що мають мiсце в реальних електронних схемах. В ключових схемах, якi використовуютьтся при двiйковому представленнi iнформацiї, значенням логiчного “0” та логічної “1” присвоюються обмеженi дiапазони напруг, що розмiщуються в iнтервалi вiд нуля до дiючої напруги живлення логiчних схем.

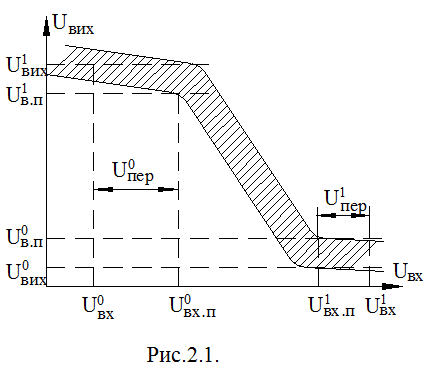

Не розглядаючи в даному параграфi технiчнi

характеристики апаратних засобiв для реалiзацiї операцiй над цифровими

сигналами, визначимось лише з основними параметрами реальних сигналiв. Якi б не

використовувались технiчнi засоби, їх параметри загалом можливо оцiнити за

допомогою характеристики UВИХ=f(UВХ) (рис. 2.1),

де, вiдповiдно, UВХ, UВИХ – напруги, що

змiнюються на входi та виходi електронного пристрою з урахуванням їх

нестабiльностi.

Не розглядаючи в даному параграфi технiчнi

характеристики апаратних засобiв для реалiзацiї операцiй над цифровими

сигналами, визначимось лише з основними параметрами реальних сигналiв. Якi б не

використовувались технiчнi засоби, їх параметри загалом можливо оцiнити за

допомогою характеристики UВИХ=f(UВХ) (рис. 2.1),

де, вiдповiдно, UВХ, UВИХ – напруги, що

змiнюються на входi та виходi електронного пристрою з урахуванням їх

нестабiльностi.

Як вiдомо, логiчнi елементи в будь-яких цифрових пристроях мають достатньо довгi послiдовнi з’єднання. Тому, проходячи вiд одного логiчного елемента до iншого, iнформацiйний сигнал може розсiювати свою енергiю. Щоб така ситуацiя не виникала, кожен логiчний елемент повинен забезпечувати пiдсилення вхiдного сигналу як по напрузi, так i по потужностi. До того ж, добре вiдомо, що функцiональна повнота логiчних елементiв обов’язково включає iнверсiю сигналу. З цього витiкає, що найпростiшим логiчним елементом може бути транзистор, включений за схемою з загальним емiтером (загальним витоком для МДН-транзисторiв), який, як відомо, інвертує вхідний сигнал. Тому зображена на рис. 2.1 дiаграма вiдображає iнверсну схему логiчного елемента.

Це фактично означає, що цифровий пристрiй повинен не тiльки формувати вихiднi сигнали з параметрами, близькими до iдеальних “0” та “1”, а й по рiвню вхiдного сигналу вiдрiзняти значення “0” та “1”.

Як рiвень логiчногого нуля, так i одиницi для будь-якого логiчного елемента є не конкретною величиною, а деяким визначеним дiапазоном напруг. Для сигналу вихiдної одиницi це дiапазон в iнтервалi вiд U1ВИХ до порогової напруги U1В.П., з якої починається перехiд цифрового елемента в iнший стан. Сигналам вихiдної логiчної одиницi вiдповiдають низькi рiвнi вхiдного сигналу U0ВХ та U0ВХ.П.. Пiд U1 та U0 розумiють номiнальнi значення напруги цифрового елемента в статичному режимi. 1Пороговi значення напруги U1П , U0П вiдповiдають найбiльшому та найменшому значенням вiдповiдних рiвнiв при яких починається перехiд логiчного елемента в iнший стан. Кiлькiсно пороговi значення визначаються точкою на характеристицi UВИХ = f(UВХ) вякiй модуль диференцiйного коефiцiєнта передачi цифрового елемента рiвняється одиницi. Пороговi рiвнi визначають стiйкiсть до перешкод логiчних елементiв. 2.Виділяються статична та динамiчна перешкодостiйкiсть. Статична перешкодостiйкiсть оцiнюється як мiнiмальна рiзниця мiж значеннями вихiдного та вхiдного сигналiв визначеного рiвня:

![]() U1ПЕР=U1ВХ – U1ВХ.П ;

U1ПЕР=U1ВХ – U1ВХ.П ;

U0ПЕР=U0ВХ.П – U0ВХ . (2.1)

З (2.1) бачимо, що статична

перешкодостiйкiсть – це мiнiмальна величина пере-шкоди на виходi цифрового

елемента, що може привести до змiни стану пiдключеного до нього логiчного

елемнта тої ж серiї. Статична перешкодостiйкiсть являється параметром, що

не залежить вiд часу, тобто 3.тривалiсть

перешкоди набагато перевищує час змiни стану ключового елемента. Якщо ж час дiї

перешкоди близький до часу пере-ключення елемента, то така перешкода

називається динамiчною.

З (2.1) бачимо, що статична

перешкодостiйкiсть – це мiнiмальна величина пере-шкоди на виходi цифрового

елемента, що може привести до змiни стану пiдключеного до нього логiчного

елемнта тої ж серiї. Статична перешкодостiйкiсть являється параметром, що

не залежить вiд часу, тобто 3.тривалiсть

перешкоди набагато перевищує час змiни стану ключового елемента. Якщо ж час дiї

перешкоди близький до часу пере-ключення елемента, то така перешкода

називається динамiчною.

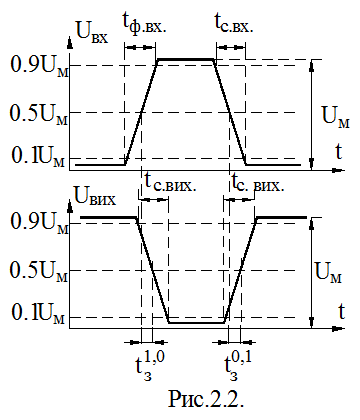

Цифровi сигнали характеризуються також часовими характеристиками, якi здебiльшого визначаються як динамiчнi параметри логiчних ключiв. До них вiдносяться:

t1,0 - час переходу виходу елемента з стану “1” в “0” – це iнтервал

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.