одинаковы по функциональному назначению относительно к их применению в устройствах. Данный предмет рассматривает электронные системы программного управления, с использование ИМС, в автоматизированном производстве. Курсовой проект по предмету «Электронные системы программного управления в автоматизированном производстве» является завершающим этапом в изучении данного предмета.

2.Общая часть

Назначение и описание принципа работы устройства.

Устройство сложения двух четырехразрядных числа- предназначено для выполнения арифметического суммирования (сложения) чисел в двоичном коде. Простейший случай- это суммирование двух одноразрядных чисел: 0+0=0; 1+1=1; 1+1=10. В последнем случае выходное число (10=2) оказалось двоичным двухразрядным. Появившаяся в старшем разряде суммы единица называется единицей переноса.

Полный сумматор много разрядных чисел составляется из полных сумматоров одноразрядных чисел. Они могут выполнять основную арифметическую операцию – суммирования много разрядных чисел двумя способами: параллельными или последовательными.

Данное мне устройство (параллельный сумматор с параллельным переносом суммирующих импульсов) – суммирует два четырёх разрядных числа (слова) А и В: разряд А1 с В1 и так далее до А4 с В4.

В каждом элементарном (одноразрядном) сумматоре получаются суммы å1…å4 и сигналы внутреннего переноса Сn+1 , которые последовательно поступают на входпереноса Сn более старшего сумматора. Выходной сигнал переноса Сn+1=С5 (единица в пятом разряде). Следовательно выходная сумма сумматора – 11111=63.

Недостатком такого параллельного сумматора является большое время распространение сигналов переноса Сn. Параллельный, без регистровый сумматор обеспечивает наибольшую скорость суммирования если снабжены схемой ускоренного переноса.

В качестве запоминающего устройства был использован регистр К555ИР23. Данные от коммутирующего узла поступают на входы D1-D8 регистра. Запись информации производится по спаду импульса отрицательной полярности на входе С. Информация на входах D1-D8 может меняться как при логическом нуле , так и при логической единице на входе С, важна она лишь непосредственно перед переходом сигнала на входе С с логического нуля в логическую единицу.

Выходы микросхемы находятся в активном состоянии, если на вход ЕО подан логический нуль. Если же на вход ЕО подать логическую единицу, выходы регистра переходят в высокоимпедансное состояние . Сигнал на входе ЕО не влияет на запись в триггеры, запись может производиться как при логическом нуле , так и при логической единице на этом входе.

3. Конструкторская часть.

Разработать структурную схему узла устройства.

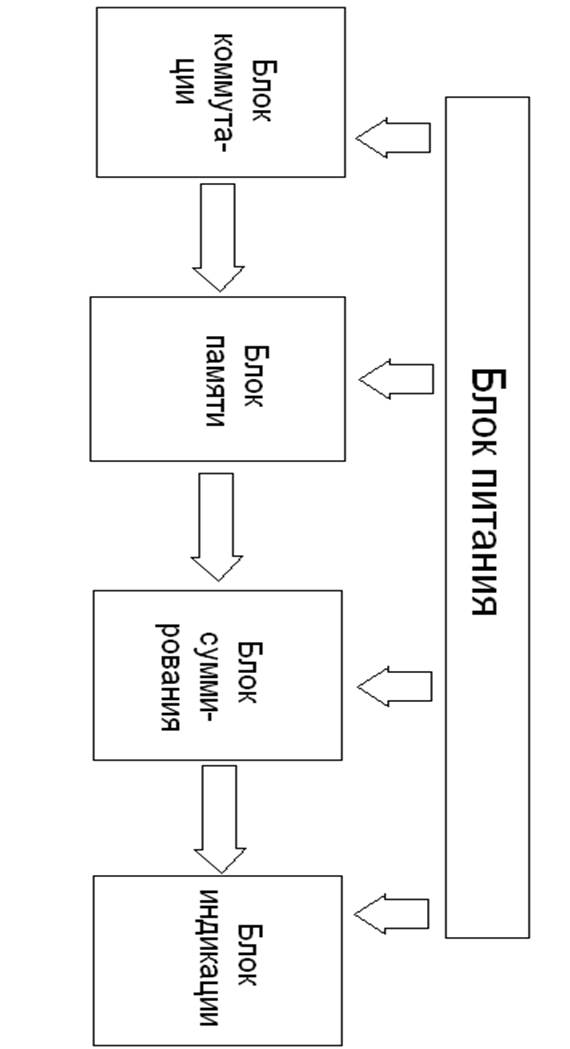

Описание структурной схемы устройства.

Структурная схема – схема , определяющая основные функциональные части изделия , их назначение и взаимосвязи.

Иными словами, структурная схема отображает принцип работы изделия в самом общем виде. На схеме изображены все основные функциональные части изделия, а также основные взаимосвязи между ними.

Согласно заданию и выбранной элементной базе была составлена следующая структурная схема, которая включает в себя следующие функциональны блоки:

1.Блок питания

2.Блок коммутации

3.Блок памяти

4.Блок суммирования

5.Блок индикации

Блок суммирования выполнен на сумматоре. Он представляет собой устройство для суммирования (сложения) чисел в двоичном коде.

Блок коммутации устройство, предназначенное для подачи входных сигналов на преобразующее устройство (в данном случае регистр).

Блок индикации построен на основе светоизлучающих диодов видимого диапазона свечения. Предназначен для индикации результатов преобразования.

Источник питания представляет собой два гальванически-развязанных стабилизированных блока питания с плавным регулированием напряжения. Предназначен для обеспечения устройства необходимыми значениями напряжения.

Блок памяти представляет собой устройство для занесения в свою память чисел , которые в свою очередь в дальнейшем поступают в блок суммирования.

Выбор и анализ элементной базы.

Для разработки данного устройства были использованы две полупроводниковые БИС: функционально завершенного СУММАТОРА типа К155ИМ3 и РЕГИСТРА К555ИР23. Сумматор предназначен для применения в электронной аппаратуре, где они осуществляют основную арифметическую операцию – суммирования чисел в двоичном коде. Микросхема выполняет функцию 4- разрядного СУММАТОРА суммирующего два четырёх разрядных двоичных числа, суммы разрядов которых появляются на выходах ∑1-∑4.

В качестве запоминающего устройства был использован регистр с восемью тактируемыми триггерами. При подаче на вход С напряжения низкого уровня разрешается запись в триггеры нового восьмибитного байта.

Для эксплуатации ИМС необходимы только один источник питания (+5В) и кнопки (предназначенные для подачи входных сигналов), а также светодиоды – для индикации суммы. Несколько СУММАТОРОВ могут взаимосвязано друг с другом, если необходимо большая разрядность входных слов.

Микросхемы К155ИМ3 изготавливают по биполярной технологии, модифицированной для совмещенного формирования на кристалле биполярных транзисторов, а также элементов инжекционной логики и тонкопленочных прецизионных резисторов. Технология позволяет разместить в одной БИС большое число цифровых элементов и выполнить аналоговые узлы с высоким уровнем параметров.

ИМС К155ИМ3 выпускаются в 16 – выводном герметичном корпусе с вертикальным расположением выводов. Сумматор работает со словами как положительной (высокий уровень – единица), так и отрицательной (низкий уровень – единица) логик. Суммирование происходит согласно уравнению:

Сn+2^0(A1+B1)+2^1(A2+B2)+2^2(A3+B3)+2^3(A3+B3)=2^0∑1+2^1∑2+2^2∑3+

+2^3∑4+2^4Cn+1.

Нумерация и назначение выводов ИМС :

Первый операнд:

1 – разряд А4(старший разряд) ;

3 – разряд А3 ;

8 – разряд А2 ;

10 – разряд А1(младший разряд) ;

Второй операнд:

16 – разряд В4(старший разряд) ;

4 – разряд В3 ;

7 – разряд В2 ;

11 – разряд В1(младший разряд) ;

Сумма:

2 – разряд ∑3 ;

6 – разряд ∑2 ;

9 – разряд ∑1(младший разряд) ;

15 – разряд ∑5(старший разряд) ;

Сигнал перенос:

13 – вход Сn ;

Уровень переноса:

14 – выход Сn+1 ;

Земля:

12 – земля ;

Питание:

5 – питание +5В ;

Параметры СУММАТОРА-К155ИМ3

Разрядность, бит – 4;

Стандартное время суммирования, нс – 23;

Потребляемый ток (от источника +5В), мА- 62;

Напряжение питания Ucc, В – +5;

Выходные логические уровни - ТТЛ

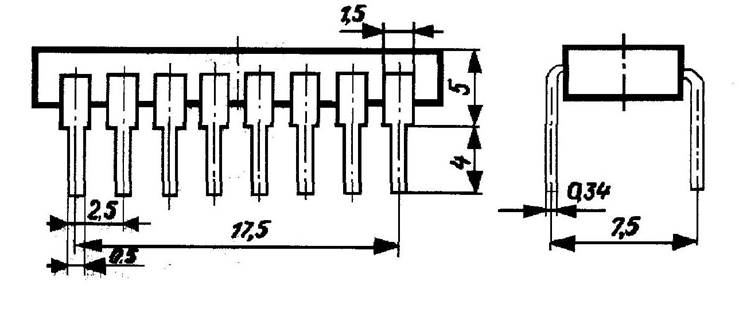

Рисунок микросхемы

К555ИР23

Микросхема К555ИР23 – восьмиразрядный регистр- защелка отображения

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.