Лекция №12 (20.10.06)

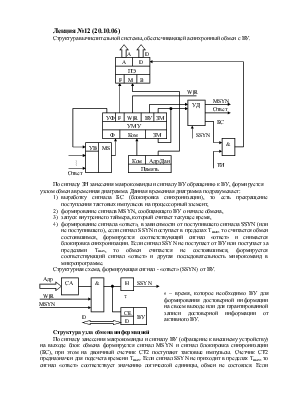

Структура вычислительной системы, обеспечивающей асинхронный обмен с ВУ.

По сигналу ЗН занесения макрокоманды и сигналу ВУ обращению к ВУ, формируется узлом обмена временная диаграмма. Данная временная диаграмма подразумевает:

1) выработку сигнала БС (блокировка синхронизации), то есть прекращение поступления тактовых импульсов на процессорный элемент,

2) формирование сигнала MSYN, сообщающего ВУ о начале обмена,

3) запуск внутреннего таймера, который считает текущее время,

4) формирование сигнала «ответ», в зависимости от поступившего сигнала SSYN (или не поступившего), если сигнал SSYN поступает в пределах Tmax, то считается обмен состоявшимся, формируется соответствующий сигнал «ответ» и снимается блокировка синхронизации. Если сигнал SSYN не поступает от ВУ или поступает за пределами Tmax, то обмен считается не состоявшимся, формируется соответствующий сигнал «ответ» и другая последовательность микрокоманд в микропрограмме.

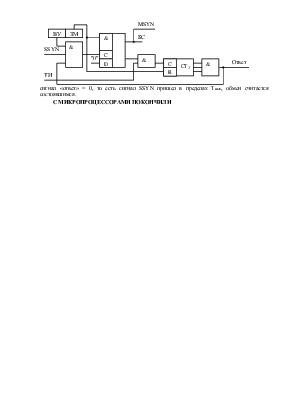

Структурная схема, формирующая сигнал - «ответ» (SSYN) от ВУ.

τ – время, которое необходимо ВУ для формирования достоверной информации на своем выходе или для гарантированной записи достоверной информации от активного ВУ.

По сигналу занесения макрокоманды и сигналу ВУ (обращение к внешнему устройству) на выходе блок обмена формируется сигнал MSYN и сигнал блокировка синхронизации (БС), при этом на двоичный счетчик СТ2 поступают тактовые импульсы. Счетчик СТ2 предназначен для подсчета времени Tmax. Если сигнал SSYN не приходит в пределах Tmax, то сигнал «ответ» соответствует значению логической единицы, обмен не состоялся. Если сигнал «ответ» = 0, то есть сигнал SSYN пришел в пределах Tmax, обмен считается состоявшимся.

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.