|

|

|

|

|

|

|

|

УОПД

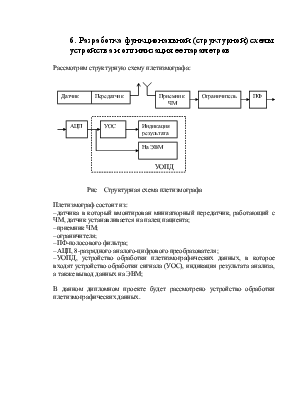

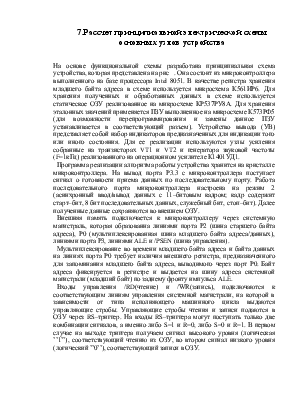

Рис Структурная схема плетизмографа

Плетизмограф состоит из:

–датчика в который вмонтирован миниатюрный передатчик, работающий с ЧМ, датчик устанавливается на палец пациента;

–приемник ЧМ;

–ограничителя;

–ПФ-полосового фильтра;

–АЦП, 8-разрядного аналого-цифрового преобразователя;

–УОПД, устройство обработки плетизмографических данных, в которое входят устройство обработки сигнала (УОС), индикация результата анализа, а также вывод данных на ЭВМ;

В данном дипломном проекте будет рассмотрено устройство обработки плетизмографических данных.

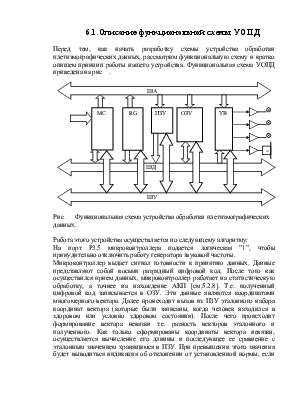

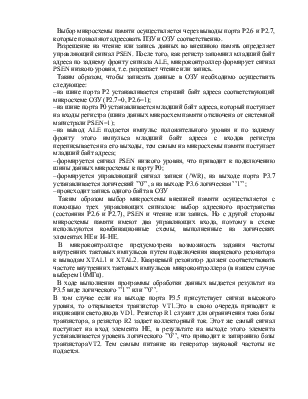

Перед тем, как начать разработку схемы устройства обработки плетизмографических данных, рассмотрим функциональную схему и кратко опишем принцип работы нашего устройства. Функциональная схема УОПД приведена на рис .

|

Рис Функциональная схема устройства обработки плетизмографических данных.

Работа этого устройства осуществляется по следующему алгоритму:

На порт Р3.5 микроконтроллера подается логическая ”1”, чтобы принудительно отключить работу генератора звуковой частоты.

Микроконтроллер выдает сигнал готовности к принятию данных. Данные представляют собой восьми разрядный цифровой код. После того как осуществился прием данных, микроконтроллер работает на статистическую обработку, а точнее на нахождение АКП [см.5.2.8]. Т.е. полученный цифровой код записывается в ОЗУ. Эти данные являются координатами многомерного вектора. Далее происходит вызов из ПЗУ эталонного набора координат вектора (которые были записаны, когда человек находился в здоровом или условно здоровом состоянии). После чего происходит формирование вектора невязки т.е. разность векторов эталонного и полученного. Как только сформированы координаты вектора невязки, осуществляется вычисление его длинны и последующее ее сравнение с эталонным значением хранящимся в ПЗУ. При превышении этого значения будет выводиться индикация об отклонении от установленной нормы, если же полученная величина не превышает порог или равна ему, то будет выводиться индикация об удовлетворительном состоянии пациента.

После сбрасывания результата обработки микроконтроллер вернется в исходное состояние и выдаст сигнал о готовности к приему следующей цифровой последовательности.

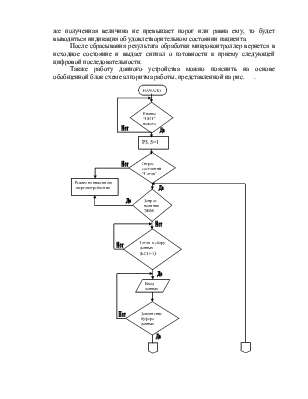

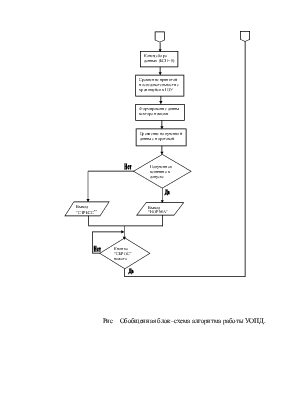

Также работу данного устройства можно пояснить на основе обобщенной блок схеме алгоритма работы, представленной на рис. .

|

![]()

![]()

|

|

Рис Обобщенная блок–схема алгоритма работы УОПД.

На основе функциональной схемы разработана принципиальная схема устройства, которая представлена на рис . Она состоит из микроконтроллера выполненного на базе процессора Intel 8051. В качестве регистра хранения младшего байта адреса в схеме используется микросхема К561ИР6. Для хранения полученных и обработанных данных в схеме используется статическое ОЗУ реализованное на микросхеме КР537РУ8А. Для хранения эталонных значений применяется ПЗУ выполненное на микросхеме К573РФ5 (для возможности перепрограммирования и замены данное ПЗУ устанавливается в соответствующий разъем). Устройство вывода (УВ) представляет собой набор индикаторов предназначенных для индикации того или иного состояния. Для ее реализации используются узлы усиления собранные на транзисторах VT1 и VT2 и генератора звуковой частоты (F=1кГц) реализованного на операционном усилителе К1401УД1.

Программа реализации алгоритма работы устройства хранится на кристалле микроконтроллера. На вывод порта Р3.3 с микроконтроллера поступает сигнал о готовности приема данных по последовательному порту. Работа последовательного порта микроконтроллера настроена на режим 2 (асинхронный ввод/вывод данных с 11–битовым кадром; кадр содержит старт–бит, 8 бит последовательных данных, служебный бит, стоп–бит). Далее полученные данные сохраняются во внешнем ОЗУ.

Внешняя память подключается к микроконтроллеру через системную магистраль, которая образованна линиями порта Р2 (шина старшего байта адреса), Р0 (мультиплексированная шина младшего байта адреса/данных), линиями порта Р3, линиями ALE и /PSEN (шина управления).

Мультиплексирование во времени младшего байта адреса и байта данных на линиях порта Р0 требует наличия внешнего регистра, предназначенного для запоминания младшего байта адреса, выводимого через порт Р0. Байт адреса фиксируется в регистре и выдается на шину адреса системной магистрали (младший байт) по заднему фронту импульса ALE.

Входы управления /RD(чтение) и /WR(запись), подключаются к соответствующим линиям управления системной магистрали, на которой в зависимости от типа исполняющего машинного цикла выдаются управляющие стробы. Управляющие стробы чтения и записи подаются в ОЗУ через RS–триггер. На входы RS–триггера могут поступать только две комбинации сигналов, а именно либо S=1 и R=0, либо S=0 и R=1. В первом случае на выходе триггера получаем сигнал высокого уровня (логическая ’’1’’), соответствующий чтению из ОЗУ, во втором сигнал низкого уровня (логический ’’0’’), соответствующий записи в ОЗУ.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.