¾ Signal Base Value =200m

¾ Flight Time – Rising Edge= 20n

¾ Flight Time – Falling Edge =20n

¾ Slope – Rising Edge =10n

¾ Slope – Falling Edge =10n

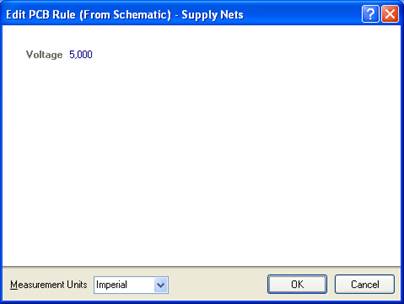

В обязательном порядке для цепей питания необходимо задать правило Place→Directives→PCBLayout →SignalIntegrity→SupplyNets с указание напряжения в этой цепи относительно напряжения в цепи GND. В данной схеме используется напряжение питания +5В, поэтому после выполнения данной команды появится окно, где задаем напряжение питание равное 5В.

Рисунок 4 - Окно для задания напряжения питания

Далее таким же образом задаем это же правило для GND равное 0В.

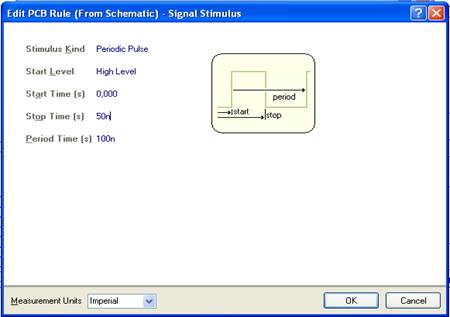

Источники сигнала и их параметры задаются с помощью выполнения команды Place→Directives→Stimulus, появляется красный значок, нажмите кнопку Tab, а потом выполните команду AddasRule→EditRuleValues. После чего из списка правил выберите SignalStimulus и произведите на этом правиле двойной щелчок по левой кнопке мыши, появится окно, где можно задать параметры сигнала. Окно для задания параметров сигнала приведено на рисунке 5

Рисунок 5 – Окно для задания параметров сигнала

Для проекта-примера задан сигнал (для цепи с1) с соответствующими параметрами: SignalStimulus [Kind- Periodiс Pulse, StartLevel – HighLevel, Start Time=0, StopTime=50n, PeriodTime=100n]

Из этой записи видно, что по данной цепи пойдет сигнал с частотой равной 10MHz и сигнал с такой частотой пойдет, только по этой цепи.

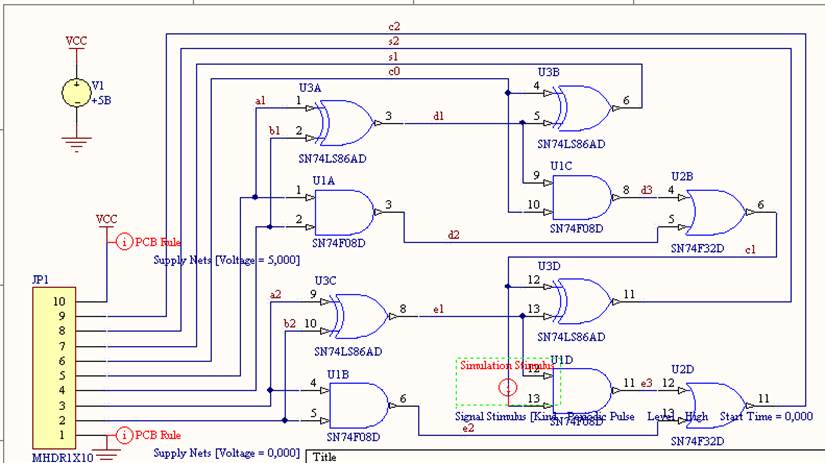

После последовательного выполнения всех действий схема-пример будет выглядеть следующим образом (рисунок 6).

Рисунок 6 – Вид схемы-примера после подготовки проекта к анализу

4. Анализ целостности сигналов на этапе проектирования топологии печатной платы (посттопологический анализ)

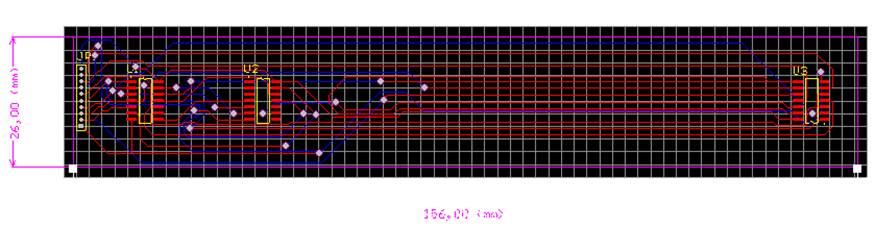

Рассмотрим последовательность выполнения анализа целостности сигналов после трассировки печатной платы. В примере топология печатной платы намеренно сделана с большими паразитными параметрами между проводниками, чтобы показать взаимовлияние проводников друг на друга. Топология формируется известными способами автоматической и ручной трассировки. Сформированная топология печатной платы примера представлена на рисунке 9. Если имеется готовая печатная плата, то при добавлении ее в проект правила, которые задавались при предтопологичесокм анализе не будут учитываться, поэтому необходимо выполнить обновление печатной платы выполнив команду Design→Import.

Рисунок 9 - Топология печатной платы примера

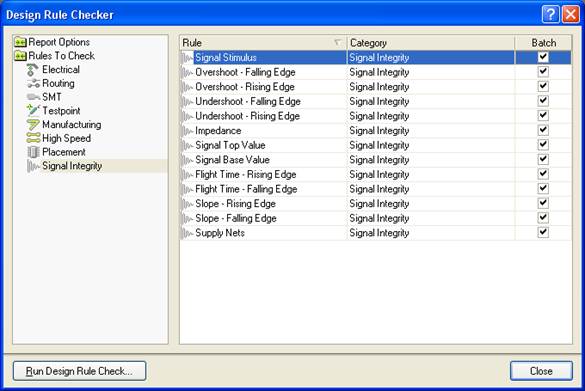

Анализ целостности сигналов при проверке правил проектирования (DRC). Для выполнения анализа необходимо, чтобы при проверке правил проектирования осуществлялась проверка правил раздела «Signal Integrity», для чего необходимо выполнить команду меню Tools→Design Rule Check, выбрать в левой части окна пункт Rules to Check→Signal Integrity, и отметить галочками в правой части окна каждое из правил (рисунок 10).

Рисунок 10 - Включение проверки правил Signal Integrity при проверке правил проектирования (DRC)

После этого, нажатием кнопки «Run Design Rule Check» запускается процедура проверки правил проектирования. Результатом работы процедуры является текстовый файл-отчёт с указанием цепей и значений параметров сигналов, которые превысили допустимые границы. Очевидно, что данный вид проверки целостности сигналов даёт только общее представление о характере происходящих процессов, а именно позволяет лишь узнать параметры этих процессов, но не позволяет определить форму сигнала.

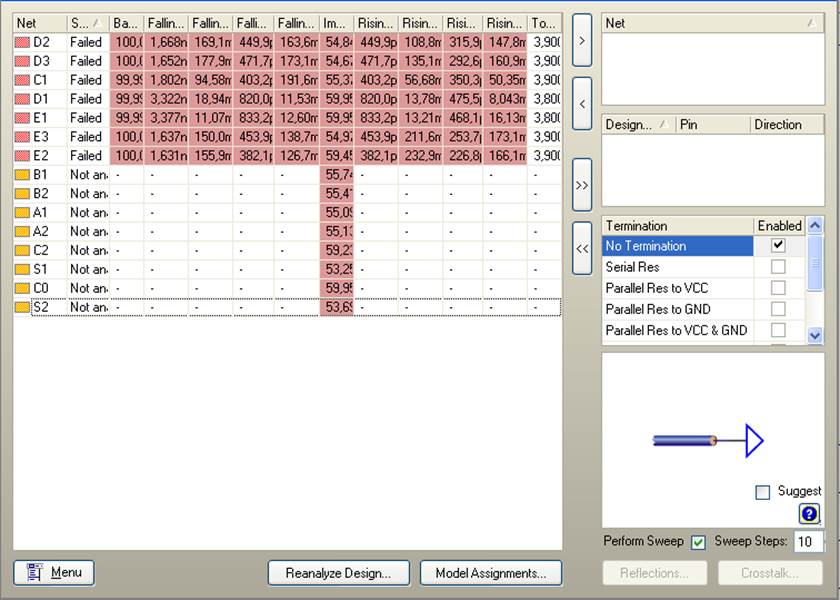

Для определения формы сигнала, а также для осуществления проверки на перекрёстные помехи необходимо запустить модуль анализа целостности сигналов из пункта меню Tools→Signal Integrity. Окно, появляющееся после выполнения этого пункта меню, похоже на окно, представленное на рисунке 4 за тем лишь отличием, что параметры у каждой цепи стали отличатся, так как сформированная топология позволяет рассчитать импеданс каждой цепи, длительность фронта и спада сигнала и другие параметры. Как и при запуске анализа из редактора схем, имеется столбец Status, функции и набор возможных значений которого ничем не отличается от описанного ранее.

Окно Signal Integrity представлено на рисунке 11.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.