|

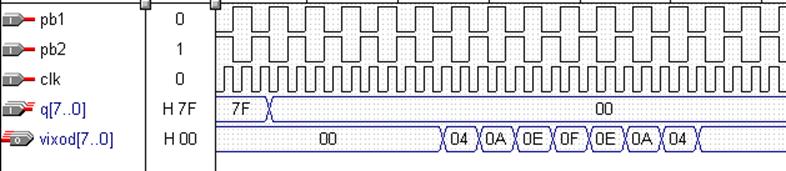

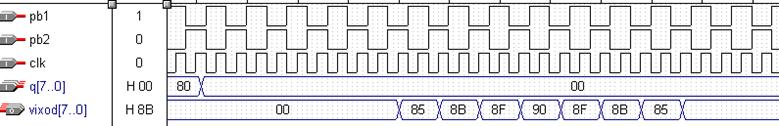

Таблица . Рассчитанные выходные отсчеты при подаче на вход фильтра -128(10)=80(16).

|

dec ai |

dec*-128 |

bin |

Bin [17-10] |

доп. код HEX |

прям. код HEX |

|

38 |

-4826 |

11110110100100110 |

11111011 |

FB |

85 |

|

81 |

-10287 |

11101011111010001 |

11110101 |

F5 |

8B |

|

115 |

-14605 |

11100011011110011 |

11110001 |

F1 |

8F |

|

127 |

-16256 |

11100000010000000 |

11110000 |

F0 |

90 |

|

115 |

-14605 |

11100011011110011 |

11110001 |

F1 |

8F |

|

81 |

-10287 |

11110110100100110 |

11111011 |

FB |

85 |

|

38 |

-4826 |

11110110100100110 |

11111011 |

FB |

85 |

Так как экспериментальное и теоретическое значение импульсной характеристики совпадают, следовательно, цифровой фильтр спроектирован верно.

7. Составление принципиальной схемы устройства и ее описание

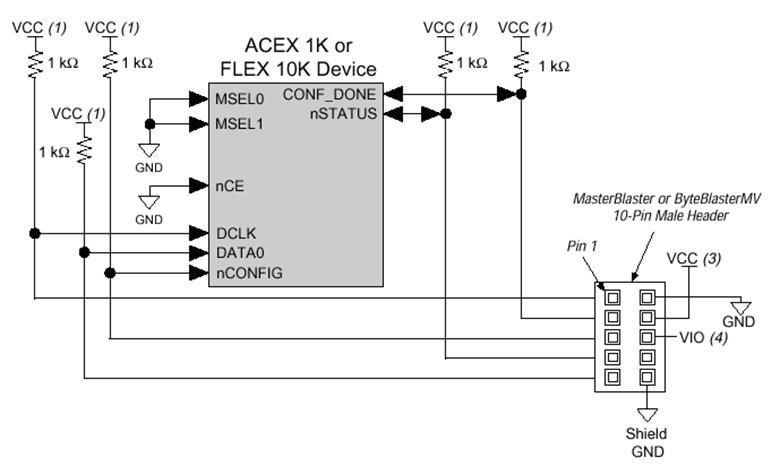

В пассивном последовательном режиме конфигурирования (Passive Serial) (PS-конфигурировании) с помощью загрузочного кабеля главный контроллер загружает данные из внешнего запоминающего устройства в микросхемуFLEX 10K через кабель MasterBlaster или ByteBlasterMV. Для начала конфигурирования в этом режиме загрузочное устройство обеспечивает изменение уровня сигнала от "0" в "1" на выводе nCONFIG. Программирующая аппаратура затем побитно передает конфигурационные данные на вывод DATA микросхемы. В микросхеме FLEX 10K используется вывод DATA0. Данные синхронно принимаются конфигурируемой микросхемой до момента перехода вывода CONF_DONE в состояние "1". FLEX 10K с использованием загрузочных устройств MasterBlaster или ByteBlasterMV.

Выводы MSEL0 и MSEL1 используются для изменения режимов конфигурирования. В обычном режиме эти выводы соединены с землей или напряжением питания VCC.

|

Логические состояния выводов |

Схема конфигурирования |

|

|

MSEL1 |

MSEL0 |

|

|

0 |

0 |

Конфигурационное ПЗУ или режим пассивной последовательной конфигурации |

|

1 |

0 |

Пассивная параллельная синхронная |

|

1 |

1 |

Пассивная параллельная асинхронная |

В пассивном последовательном режиме конфигурирования выводы MSEL0 и MSEL1 соединены с землей.

На вывод 6 разъема подается опорное напряжение VIO выходного буфера MasterBlaster. Напряжение VIO должно быть согласовано с напряжением VCCIO. Для MasterBlasterMV этот вывод оставляется несоединенным. Контакты микросхемы, подключенные к +5В заземляются через конденсаторы 0,1мкФ, непосредственно рядом с корпусом микросхемы. Контакт разъема +5В заземляются через конденсатор 10мкФ.

[Использована литература № 3]

8. Заключение

В данном курсовом проекте был спроектирован цифровой фильтр низкой частоты, удовлетворяющий техническому заданию. Была разработана принципиальная схема фильтра, а также была разработана и отлажена программа на языке AHDL. Аппаратная часть по возможности была минимизирована для улучшения быстродействия и уменьшения аппаратных затрат.

9. Список использованных источников

1. Ашихмин А. С. Программируемые логические интегральные схемы (часть I): Учеб. Пособие; Рязан. Гос. Радиотехн. Акад. Рязань, 2005. 88 с.

2. Антонов А.П. Язык описания цифровых устройств Altera AHDL. :Практический курс. -М., :Радио Софт, 2001г

3. Конфигурирование ПЛИС Altera со статической памятью конфигурации. Учебное пособие. /Под ред. В. В. Мяльк. Кафедра радиотехнических систем Санкт-Петербургского Государственного университета аэрокосмического приборостроения. Санкт-Петербург 2003г

4.Раздаточный материал ПЛИС

10. Приложение

Преобразователь кода.

Преобразует входной параллельный 8-ми разрядный прямой код в параллельный 8-ми разрядный дополнительный код

-- Выполнил студент гр. 310 Алёшином Р.И.

-- Преобразователь кода

SUBDESIGN preobr

( reset : INPUT = GND;

setn : INPUT = VCC;

clock_en : INPUT = VCC;

clk : INPUT ;

vxod[7..0] : INPUT ;

vyxod[7..0] : OUTPUT; )

VARIABLE

tr[7..0] : dffe ;

BEGIN

tr[].(CLK, CLRN, PRN, ENA) = (clk, !reset, setn, clock_en);

IF vxod[7] THEN

tr[].d = (vxod[7], -vxod[6..0]);

ELSE

tr[].d = vxod[7..0];

END IF;

vyxod[7..0] = tr[].q;

END;

Сдвигающий регистр

Для сдвига полученных регистров и обеспечения задержки.

--- Выполнил студент гр. 310 Алёшин Р.И.

--- Программа cдвигающего регистра

PARAMETERS

( width=8,

number=7 );

SUBDESIGN reg_sdvig

( clk : INPUT ;

clock_en : INPUT = VCC;

reset : INPUT = GND;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.