Содержание

1. Техническое задание. 3

2. Анализ технического задания. 4

3. Распределение адресного пространства. 6

4. Описание принципиальной схемы.. 7

5. Перечень элементов. 10

6. Программа. 11

7. Алгоритм работы программы.. 14

8. Список литературы.. 15

Разработать фильтр

сигнала с возможностью передачи данных на ПК по RS-232

(амплитуды входного и выходного сигналов) работающий по следующему алгоритму: ![]()

По требованию технического задания необходимо разработать цифровой фильтр на основе микропроцессорной системы (МПС). Для достижения поставленной задачи необходимо предусмотреть установку помимо стандартных составных частей МПС (микропроцессора (МП), ПЗУ, ОЗУ, тактового генератора) следующие необходимые компоненты:

1) Устройство считывания внешнего сигнала и преобразования его в двоичный код (АЦП);

2) Утройство преобразующее полученный результат в аналоговую форму (ЦАП);

3) Устройство, вызывающее считывание и обработку данных микропроцессором с заданным Tд (таймер К1810ВИ54);

4) Средство передачи данных по RS-232 (последовательный интерфейс КР580ВВ51А).

Рассмотрим каждую составляющую МПС более детально.

В качестве МП воспользуемся микросхемой К1810ВМ86, выполненной по n-МОП технологии, имеющей 16-разрядную шину данных (ШД) и 20-разрядную шину адреса (ША), мультиплексированную с ШД. Этот МП может работать на тактовой частоте до 5МГц и взаимодействовать с внешними устройствами на ТТЛ-уровнях. Блок центрального процессора включает в себя: буферные регистры для защелкивания адреса, двунаправленные шинные формирователи ШД и дешифратор сигналов управления запоминающими и внешними устройствами.

ПЗУ представлено двумя микросхемами К573РФ2 по 2КБ каждая. В нем будет записана программа управления МПС и вектор обработки прерывания.

В ОЗУ будут храниться некоторые переменные и адрес возврата из подпрограммы обработки прерывания. ОЗУ будет организовано двумя микросхемами К537РУ9А по 2КБ каждая.

В качестве АЦП будет использоваться 10-разрядная микросхема К1113ПВ1, способная работать в двухполярном режиме с напряжением на входе ±5.12В. АЦП будет принимать входной сигнал, преобразовывать его в двоичный код и по шине данных передавать его в микропроцессор для дальнейшей обработки.

12-разрядный ЦАП К1108ПА1 способен работать в двухполярном режиме с максимальным напряжением на выходе ±1В (без внешнего ОУ). Задачей ЦАП будет считывание из буферного регистра двоичного кода найденной амплитуды сигнала, преобразование его в аналоговую форму и передача внешнему устройству.

Для связи с внешним компьютером будет использован последовательный интерфейс КР580ВВ51А работающий в асинхронном режиме 8N1. По нему будут передаваться амплитуда входного и выходного сигналов.

Таймер К1810ВИ54 будет выполнять 2 функции: формирование запросов прерываний процессора с частотой 1/Tд и формирование частоты синхронизации передатчика КР580ВВ51А.

В качестве генератора тактовых импульсов воспользуемся микросхемой К1810ГФ84 с внешней резонаторной цепью на 15МГц.

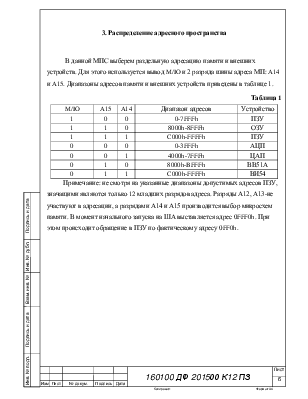

В данной МПС выберем раздельную адресацию памяти и внешних устройств. Для этого используется вывод M/IO и 2 разряда шины адреса МП: A14 и A15. Диапазоны адресов памяти и внешних устройств приведены в таблице 1.

Таблица 1

|

M/IO |

A15 |

A14 |

Диапазон адресов |

Устройство |

|

1 |

0 |

0 |

0-7FFFh |

ПЗУ |

|

1 |

1 |

0 |

8000h-8FFFh |

ОЗУ |

|

1 |

1 |

1 |

C000h-FFFFh |

ПЗУ |

|

0 |

0 |

0 |

0-3FFFh |

АЦП |

|

0 |

0 |

1 |

4000h-7FFFh |

ЦАП |

|

0 |

1 |

0 |

8000h-BFFFh |

ВВ51А |

|

0 |

1 |

1 |

C000h-FFFFh |

ВИ54 |

Примечание: не смотря на указанные диапазоны допустимых адресов ПЗУ, значащими являются только 12 младших разрядов адреса. Разряды А12, А13-не участвуют в адресации, а разрядами А14 и А15 производится выбор микросхем памяти. В момент начального запуска на ША выставляется адрес 0FFF0h. При этом происходит обращение в ПЗУ по фактическому адресу 0FF0h.

Разрабатываемая МПС является однопроцессорной: система имеет сравнительно небольшое число ИС и ВУ, МП работает в минимальном режиме, то есть все необходимые сигналы управления периферийными устройствами вырабатываются на основе управляющих сигналов МП: #WR, #RD и M/IO (символ # означает инверсный сигнал).

Задача демультиплексирования (разделения) ША и ШД решается с помощью буферных регистров и шинных формирователей.

Восьмиразрядные буферные регистры КР580ИР82 используются в качестве однонаправленных шинных формирователей (адресных защелок), так как адресная информация должна быть выставлена в течение всего цикла чтения/записи. Защелкивание адреса осуществляется перепадом 0-1 на входе STB.

Для организации ШД используются двунаправленные восьмиразрядные шинные формирователи с высокой нагрузочной способностью КР580ВА86, режим работы которых определяется управляющими сигналами, поступающими с МП: Т(направление передачи) и #ОЕ (разрешение передачи).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.