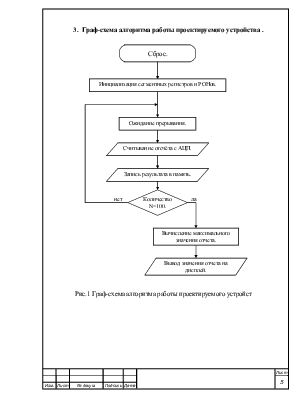

производиться запись отчетов с АЦП, но имеются данные о времени преобразования АЦП. Предположим, что это и есть интервал времени между записью октетов. В задании также сказано, что необходимо организовать программный запуск АЦП, следовательно отпадает необходимость в использовании программируемого таймера в нашей МПС.

Сигнал “запрос прерывания” формируется АЦП после окончания преобразования.

Считанные с АЦП значения записываются в ОЗУ.

После окончания снятия отчетов, вычисляется максимальный по амплитуде отчет и затем выводится на цифровой дисплей с помощью контроллера клавиатуры и дисплея (ККД).

Для построения микропроцессорной системы будем использовать ЦПУ КР1810ВМ86, имеющее 16-разрядную шину данных, что позволит напрямую передавать 10-и разрядную информацию с АЦП, выполненное по n-МОП-технологии и электрически совместимое с микросхемами ТТЛ и ТТЛШ.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

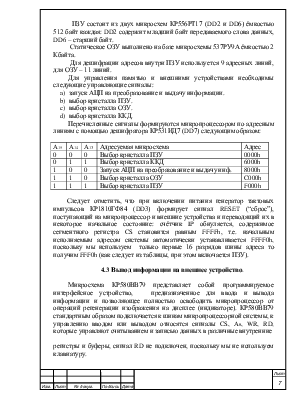

Так как проектируемое устройство состоит только из одного процессора, и число сопрягаемых с ним устройств невелико, ВМ86 работает в минимальном режиме. Стандартным образом к микропроцессору подключается генератор тактовых импульсов К1810ГФ84. К его входу RES подключена RC-цепочка, которая формирует сигнал сброса автоматически при включении питания либо с помощью кнопки SA1.

Частота опорного генератора задается с помощью внешнего кварцевого резонатора частотой 12МГц, который подключается к выводам Х1 и Х2. Тактовый сигнал МОП-уровня CLK, подаваемый на вход CLK МП, в три раза меньше частоты опорного генератора и составляет FCLK=4МГц. Внутренний делитель частоты формирует выходные импульсы PCLK скважностью 2 с частотой, равной ½ частоты сигнала CLK и обеспечивает управление устройствами, работающими на ТТЛ - уровнях.

При разработке структуры блока ЦП необходимо решить задачи разделения (демультиплексирования) шины адреса/данных, буферирования шины адреса и шины данных, а также задачу формирования системных управляющих сигналов для внешних устройств.

Первая задача решается с помощью ИС К580ИР82 (DD1 и DD5), выполняющих функции адресной защёлки, так как адресная информация должна быть выставлена в течение всего цикла чтения или записи.

DD1 защёлкивает младшие 8 бит ША, DD5 – старшие.

Вторая задача решается с помощью двунаправленных 8-битовых шинных формирователей К580ВА86 (DD9 и ВВ9), которые усиливают сигналы системной шины данных.

Т.к. в МПС ввод – вывод организован с отображением на память, то в качестве управляющих сигналов используются сигналы M/IO, WR, RD и INTA, вырабатываемые МП.

При подключении ЗУ к шинам МПС необходимо обеспечивать передачу как двухбайтовых слов, так и отдельных байтов.

При чтении из ПЗУ в любом случае происходит передача слова, поэтому сигналы BHE разрешения старшего байта и A0 на ПЗУ не подаются, а микропроцессор сам выбирает, какой байт ему нужен, старший

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.