|

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

РЯЗАНСКИЙ ГОСУДАРСТВЕННЫЙ РАДИОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

КАФЕДРА РАДИОТЕХНИЧЕСКИХ СИСТЕМ

|

к курсовому проекту по дисциплине:

на тему: Полосовой фильтр

Рязань 2006 г.

Рязань 2006 г.

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

РЯЗАНСКИЙ ГОСУДАРСТВЕННЫЙ РАДИОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра радиотехнических систем

ЗАДАНИЕ НА КУРСОВОЙ ПРОЕКТ

По дисциплине «Проектирование цифровых устройств средств РЭБ»

Студент Белокуров Е.В. код 310fir03 группа 310 _

1. Тема Полосовой фильтр

2. Срок представления проекта к защите « 4 » декабря 2006 г.

3. Исходные данные для проектирования:

3.1. Линейное разностное уравнение фильтра:

3.2. Порядок

фильтра: M = 11

3.2. Порядок

фильтра: M = 11

3.3. Коэффициенты фильтра:

|

i |

аi |

4 |

-0.31829 |

8 |

-0.31829 |

|

1 |

-3.45267Е-4 |

5 |

3.45267Е-4 |

9 |

-3.45267Е-4 |

|

2 |

-4.88224Е-4 |

6 |

0.500459 |

10 |

-4.88224Е-4 |

|

3 |

-3.45267Е-4 |

7 |

3.45267Е-4 |

11 |

-3.45267Е-4 |

3.4. Разрядность коэффициентов: 12

3.5. Входной код: параллельный прямой

3.6. Разрядность входных данных: 8

3.7. Выходной код: параллельный прямой

3.8. Разрядность выходных данных: 8

3.9. Ввод данных: по сигналу готовности

3.10. Вывод данных: по сигналу готовности

3.11. Тактовая частота синхронизации: 25,175 МГц

3.12. ПЛИС: ЕPF10K20RС240-4 (семейство FLЕX10K фирмы Аltеrа)

4. Содержание пояснительной записки курсового проекта

4.1. Титульный лист

4.2. Задание на курсовой проект

4.3. Содержание

4.4. Введение (постановка задачи)

4.5. Анализ и формализация задачи (определение полного набора функций

устройства и способов их реализации)

4.6. Разработка и обоснование структурной схемы устройства

4.7. Разработка программы на языке АHDL

4.8. Оценка быстродействия устройства

4.9. Отладка разработанной программы. Результаты отладки

4.10. Составление принципиальной схемы устройства и ее описание

4.11. Заключение

4.12. Список использованных источников

4.13. Приложение

5. Перечень графического материала: схема принципиальная электрическая _

|

|

|

|

Содержание.

|

1. Введение (постановка задачи)….…………………………… 2. Анализ и формализация задачи (определение полного набора функций устройства и способов их реализации)….. 3. Разработка и обоснование структурной схемы устройства 4. Разработка программы на языке АHDL………..…………... 5. Оценка быстродействия устройства………………………... 6. Отладка разработанной программы. Результаты отладки... 7. Составление принципиальной схемы устройства и её описание……………………………………………………… 8. Заключение……………………..……………………………. 9. Список использованных источников………….…………… 10. Приложение….………………………………………………. |

5 6 10 11 15 16 17 18 19 20 |

1. Введение (постановка задачи).

В данном курсовом проекте необходимо спроектировать полосовой фильтр, отвечающий требованиям технического задания. Требуется разработать структурную схему устройства, программу на языке АHDL и составить принципиальную схему устройства. Также необходимо провести оценку быстродействия устройства и правильность его работы по полученным характеристикам.

Проектирование проводится для выбранной ПЛИС: ЕPF10K20RС240-4(семейство FLЕX10K фирмы Аltеrаю).

Микросхемы из данного семейства в настоящее время являются одной из наиболее распространённой элементарной базы для реализации алгоритмов цифровой обработки сигналов, построения устройств обработки данных и интерфейсов. Это достигается большей логической емкостью, более удобной архитектурой, включающей встроенные блоки памяти(EBA), высокой надёжности.

Всего на микросхеме 144

логических блока соответственно 1152 логических ячеек. Для реализации фильтра

было использовано всего 187 логических ячеек.

2.Анализ

и формализация задачи (определение полного набора функций устройства и способов

их реализации).[1]

Для проектирования полосового фильтра, согласно требованиям ТЗ используется ПЛИС семейства FLEX10K фирмы ALTERA: EPF10K20RC240-4.

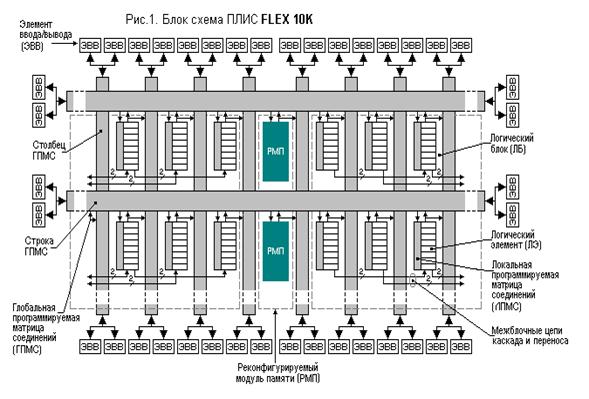

В основе архитектуры лежат логические блоки (ЛБ), содержащие 8 ЛЭ и локальную матрицу соединений. Глобальная матрица соединений разделена на строки и столбцы и имеет непрерывную структуру (Fаst Trасk Intеrсоnnесt). Посередине строки располагаются встроенные блоки памяти (ЕАB).

Наличие ЕАB позволяет делать табличную реализацию таких устройств как умножители, АЛУ, сумматоры и т.п.

Все ПЛИС этого семейства совместимы по уровням с шиной PСI, имеют возможность как последовательной, так и параллельной загрузки, полностью поддерживают стандарт JTАG который и будет использован. Общая схема ПЛИС приведена на рис.1.[4]

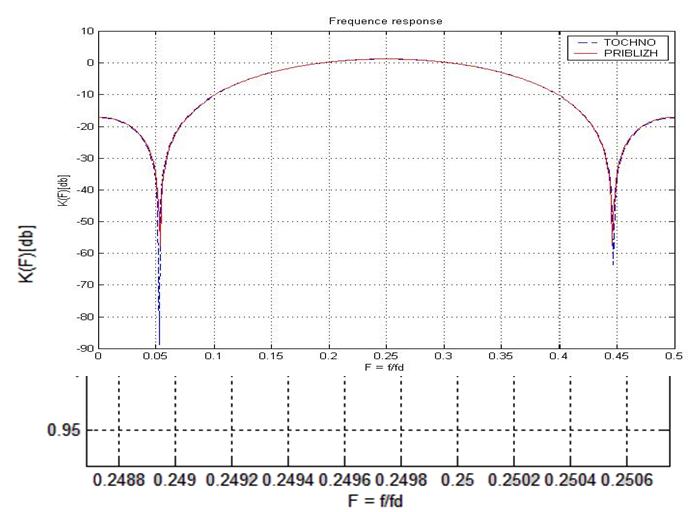

Проектируемый фильтр всего должен обеспечивать заданную АЧХ. По рисунку

видно что точная и приближенная характеристики практически не различаются, что

свидетельствует о слишком высокой разрядности коэффициентов - 12, то есть

необходимую точность можно обеспечить более низкой разрядностью коэффициентов –

9, хотя и это не предел, благодаря урезанию можно получить ощутимый выигрыш в

ресурсах ПЛИС.

|

Исходные коэффициенты:

|

i |

аi, DЕС |

аi*2^12 |

ai, DEC |

аi,HЕX |

аi,BIN |

|

1 |

-3.45267Е-4 |

-1.414213632 |

-1 |

FFF |

111111111111 |

|

2 |

-4.88224Е-4 |

-1.999765504 |

-2 |

FFЕ |

111111111110 |

|

3 |

-3.45267Е-4 |

-1.414213632 |

-1 |

FFF |

111111111111 |

|

4 |

-0.31829 |

-1303.71584 |

-1304 |

АЕ8 |

110101110100 |

|

5 |

3.45267Е-4 |

1.414213632 |

1 |

1 |

000000000001 |

|

6 |

0.500459 |

2049.880064 |

2050 |

802 |

100000000010 |

|

7 |

3.45267Е-4 |

1.414213632 |

1 |

1 |

000000000001 |

|

8 |

-0.31829 |

-1303.71584 |

-1304 |

АЕ8 |

101011101001 |

|

9 |

-3.45267Е-4 |

-1.414213632 |

-1 |

FFF |

111111111111 |

|

10 |

-4.88224Е-4 |

-1.999765504 |

-2 |

FFЕ |

111111111110 |

|

11 |

-3.45267Е-4 |

-1.414213632 |

-1 |

FFF |

111111111111 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.