24 вывода.

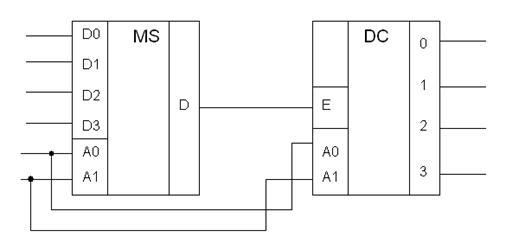

· DC 2 в 4

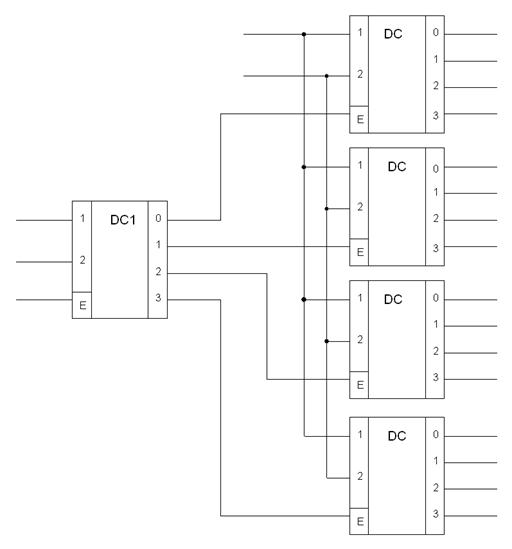

КАСКАДИРОВАНИЕ DC

Рис. 15. Каскадное соединением

DC подключены параллельно, следовательно, работают одинаково.

DC1 включает только один из четырех оставшихся DC.

Таким образом, на основе DC 2 в 4 сделали DC 4 в 16.

Подадим на Е разрешающую 1, а на остальные входы сигнал 10 (двоичная двойка). Увидим, что второй выход у DC1 будет “работать”, то есть на нем будет 1, а на остальных выходах – 0. Следовательно, 9 вывод будет активным, то есть, получаем на выходе число 9.

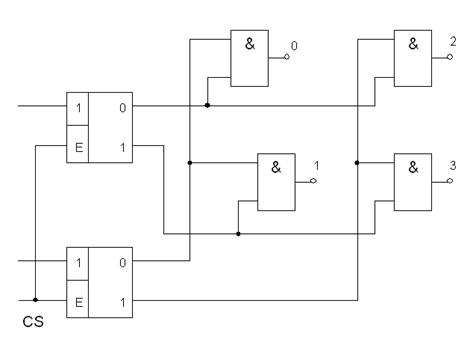

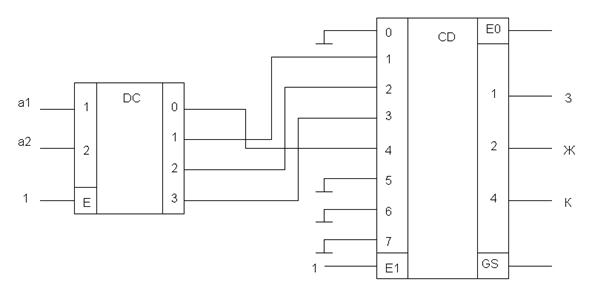

Матричный DC реализуется на базе DC 1 в 2 и получаем DC 2 в 4. (рис. 16)

CS – “выбор кристалла”, вход Е по другому.

Чтобы включить подаем 1 на вход Е.

Рис. 16. Матричный DC

Мультиплексоры

Мультиплексор – устройство, предназначенное для выбора и передачи информации с нескольких входов на один выход.

(на схемах обозначается как - MS)

Виды мультиплексоров:

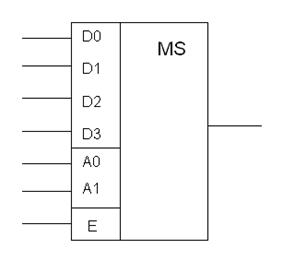

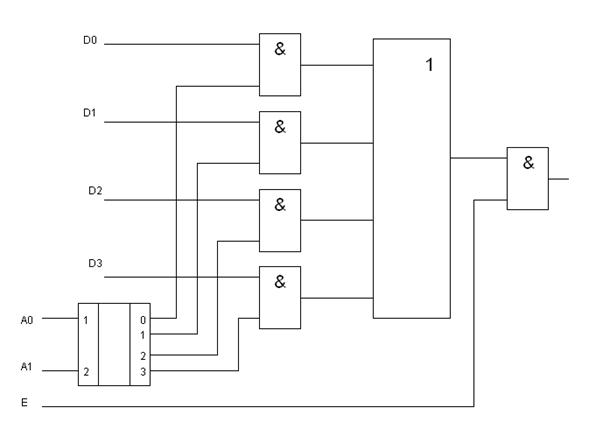

· мультиплексор 4 в 1 (рис. 17).

Рис. 17. Мультиплексор 4 в 1

D – информационный вход

А – адресный вход

Кодовая комбинация на адресных выводах определяет номер входного канала, с которого передается информация на выход.

Вход Е может быть, а может и не быть.

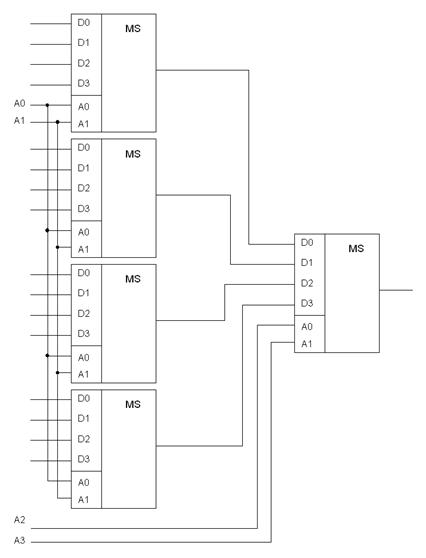

· MS 16 в 1

КР1533КП1

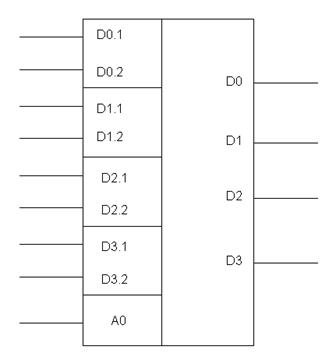

На базе MS 4 в 1 можно создать MS 16 в 1 (рис. 18).

Рис. 18. MS 16 в 1

· MS 2 в 1

КР1533КП11

· MS 8 в 1

Построение MS с помощью DC приведено на рисунке 19.

Рис. 19. MS на основе DC

Многие MS (рис. 20) используются в микросхемах памяти. Эти “маленькие”, составные MS работают параллельно. Это MS 2 в 1. Здесь осуществляется разделение большого массива адресных линий по времени и пополам.

Рис. 20.

Демультиплексоры

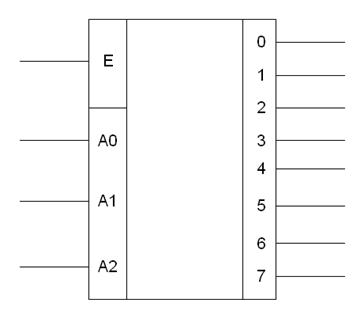

Демультиплексор – устройство, которое должно входной сигнал распределять на выход, заданный адресом (рис. 21).

Рис. 21. Демультиплексор

Задаем адрес, подаем сигнал, например, 101 и он появляется на данном выходе. В нашем случае на 5 выходе (так как 101 это 5). Видно, что демультиплексор – это дешифратор, если на адресные входы подать код числа, а Е – вход разрешения.

Рассмотрим несколько примеров:

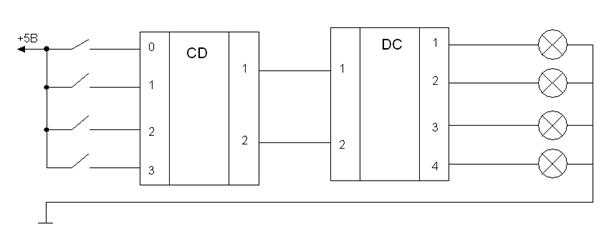

1. например, нужно зажечь несколько лампочек (рис. 22)

Рис. 22.

2. передача информации (рис. 23).

Рис. 23.

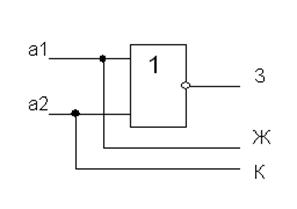

3. преобразование произвольных кодов на примере светофора (рис. 24).

|

а1 |

а2 |

з |

ж |

к |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

fз

= ![]()

fж

= ![]()

fк

= ![]()

Рис. 24. Светофор в базисе 2 И НЕ

Если в базисе 2 ИЛИ НЕ (рис. 25):

fз

= ![]()

fж = а2

fк = а1

Рис. 25. Светофор в базисе 2 ИЛИ НЕ

Схема с использованием DC и CD будет выглядеть следующим образом: рис. 26.

Рис. 26. Светофор на основе DC и CD

Суммирующие и вычитающие устройства

Сумматоры

Сумматоры выполняют арифметическое сложение и вычитание чисел.

а + b = S

а, b – числа

S – сумма

Возможен перенос в старший разряд – CR

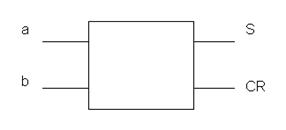

Одноразрядный полусумматор показан на рис. 27.

Рис. 27. Одноразрядный полусумматор

Таблица истинности представлена в таблице 2.

Таблица 2

|

а |

b |

S |

CR |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

S = ![]()

CR = а∙b

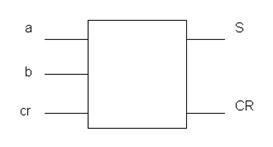

Сумматор показан на рис. 28.

Рис. 28. Сумматор

cr – выход в старший разряд

Таблица истинности представлена в таблице 3.

Таблица 3

|

а |

b |

Сr |

S |

CR |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

S = ![]()

CR = ![]()

Многоразрядные сумматоры

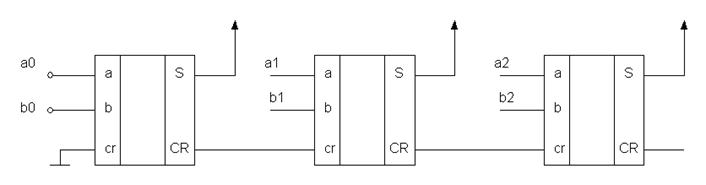

· Сумматор с последовательным переносом – рис. 29

Рис. 29. Сумматор с последовательным переносом

У сумматоров существует задержка результатов. Чем больше разрядов, тем больше задержка. Это из-за последовательного включения переноса.

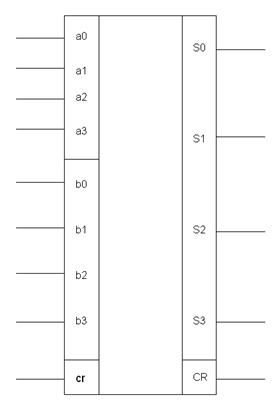

Условное обозначение сумматора показано на рис. 30.

Рис. 30. Обозначение сумматоров

· Сумматор с параллельным переносом

С точки зрения суммы разницы между сумматором с параллельным переносом и с последовательным переносом нет.

С точки зрения переноса: у сумматора с параллельным переносом перенос формируется значительно быстрее, чем с последовательным.

Способ реализации многоразрядного сумматора.

Составляем таблицу истинности (таблица 4).

Таблица 4

|

а3 |

а2 |

а1 |

а0 |

b3 |

b2 |

b1 |

b0 |

cr |

S3 |

S2 |

S1 |

S0 |

CR |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

∙ |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Вычитатели

Таблица истинности для вычитателя (таблица 5).

Таблица 5

|

а |

b |

ν |

D |

V |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

ν – заем в младший разряд

D – разность

V – заем из старшего разряда

D = ![]()

V = ![]()

Компаратор

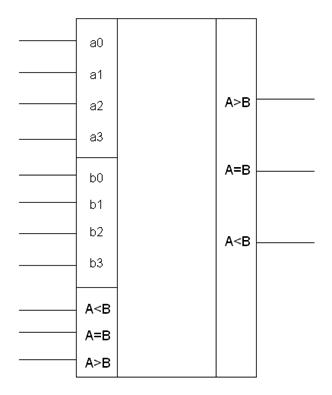

Компаратор – устройство, которое сравнивает два числа одинаковой разрядности и результатом сравнения является три сигнала.

· Последовательное каскадирование (рис. 31).

Рис. 31. Последовательное каскадирование

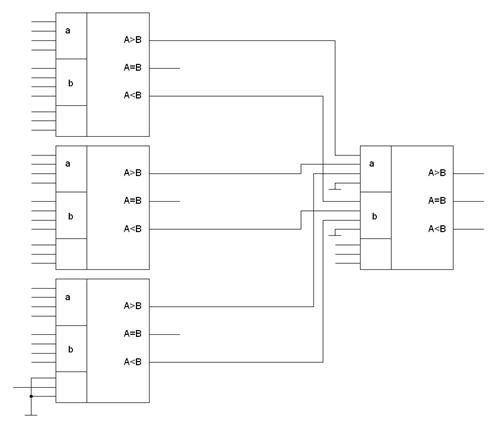

· Параллельное каскадирование (рис. 32).

Рис. 32. Параллельное каскадирование

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.