4. Разработка принципиальной схемы

4.1. РАСЧЕТ блокА предваительной выборки

канала измерения.

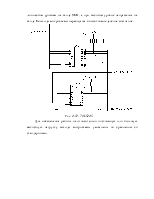

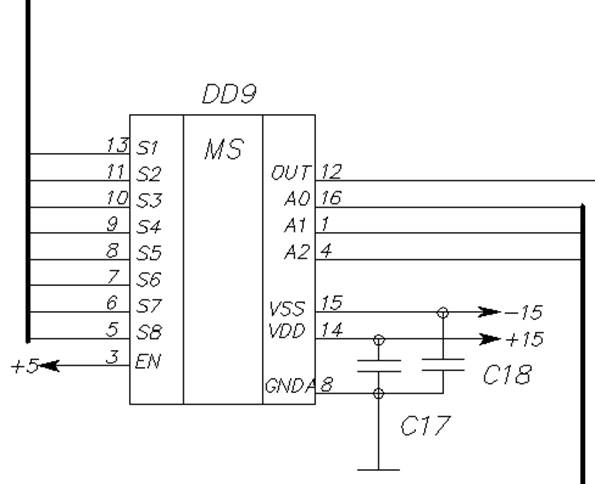

Рис.4.1. Блок предварительной выборки канала.

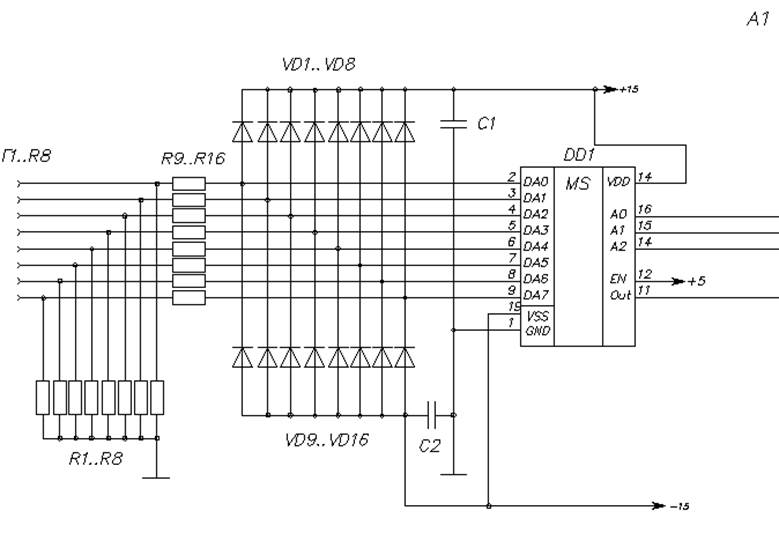

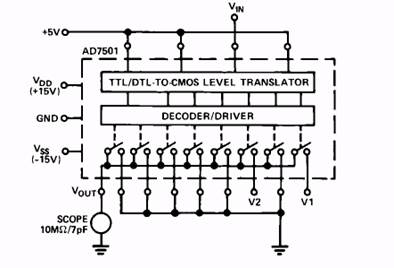

AD7501 представляет собой аналоговый мультиплексор с 8 каналами (рис. 4.2), выполненный по CMOS-технологии, который переключает один из 8 входов к выходу в зависимости от управляющего слова поступающего на три входа управления (рис. 4.3) и вход "разрешения". Все цифровые входы - TTL/DTLCMOS совместимая логика.

Рис.4.2. Внутренняя структура AD7501.

Таблица 4.1.

Таблица состоянийAD7501

На входах мультиплексоров стоят делители (R8=1 МОм и R9=15 кОм), которые обеспечивают коэффициент деления Кдел=66.

Каждый вход мультиплексора через диоды 1N4001 идет на +15В и -15В. Это нужно для защиты от подачи на входы мультиплексоров напряжения более 15В. Когда на вход подаётся напряжение более 15В, то возникает разность потенциалов и диоды открываются, замыкаясь на землю.

Выбираем элементы:

- VD1-VD128 выберем 1N4001.

- R1-R8, R17-R24, R33-R40, R49-R56, R65-R72, R81-R88, R97-R104, R113-R120 выберем МЛТ 0,125 1 МОм Е24 -2%

- R9-R16, R25-R32, R41-R48, R57-R64, R73-R80, R89-R96, R105-R112, R121-R128 выберем МЛТ 0,125 15 кОм Е24 -2%

- С1- С16 К57-3 0,1 мкФ 20 В -10%

- DD1-DD8 AD7501

4.2. РАСЧЕТ блокА выборки конечного

канала измерения.

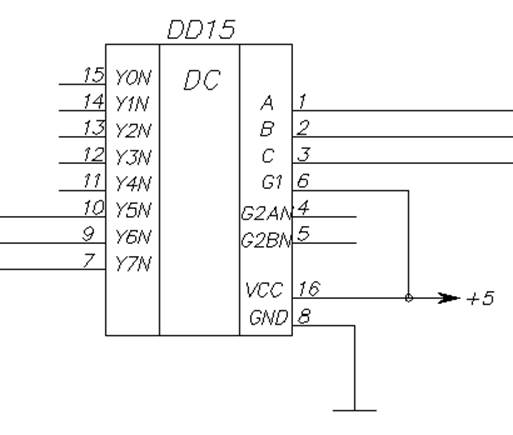

Блок конечной выборки канала измерения реализован подобно предыдущему блоку. Он также выполнен на мультиплексоре от Analog Devices AD7501 (рис. 4.4) и работает по такому же принципу: путем записи управляющего слова в A0, А1, А3 происходит выборка канала.

Рис.4.4. Блок конечной выборки канала.

Для этого блока выберем следующие элементы:

- С17 и С18 К57-3 0,1 мкФ 20 В -10%

- DD9 AD7501

Конденсаторы для этого и предыдущего блока нужны для реализации стандартной схемы включения мультиплексора.

4.3. РАСЧЕТ блокА управления.

Т.к. моё устройство работает через порт CENTRONICS в два этапа, чтение и запись, то нам необходимо блок, который бы включал режим записи и чтения для прибора. Этот блок реализован на 74LS138N – дешифраторе-мультиплексоре (рис. 4.5).

Рис.4.5. Блок управления.

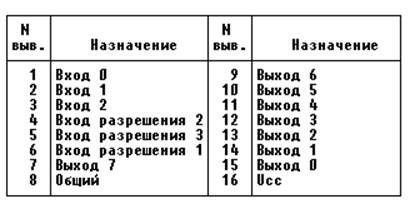

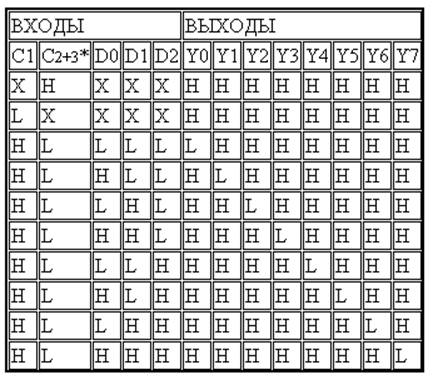

74LS138 – высокоскоростной CMOS маломощный дешифратор (рис. 4.6). Микросхема имеет три двойных входа выбора (АО, A1 и A2) и восемь выходов. Когда на разрешающем входе высокий уровень, то эти входы определяют, состояние выходов, что показано на таблице истинности (рис. 4.7).

рис. 4.6 Цоколёвка 74LS138N.

Таблица 4.2.

Таблица состояний 74LS138N

Н- высокий логический уровень

L- низкий логический уровень

Х- не используется

Таким образом, мы видим, что, записывая управляющее слово в порт мы или отдаем сигнал на DD14, которая выставляет номер канала на DD9 и на предварительный выбор на одну из микросхем DD1-DD8 а так же устанавливает коэффициент деления на DD10, или запускаем АЦП на преобразование. Работа микросхем на программном уровне будет рассмотрена ниже.

Выберем элементы:

- DD15 74LS138N.

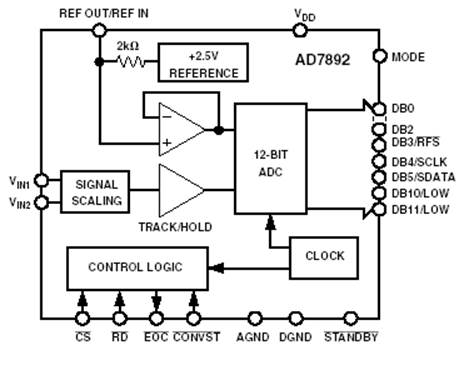

4.4. РАСЧЕТ блокА управления чтением/записью.

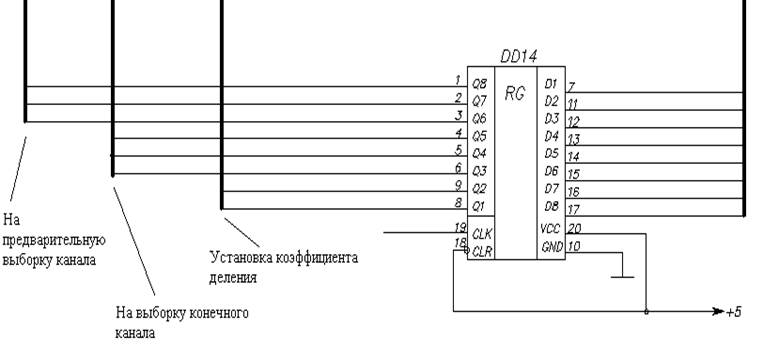

Для DD14, которая является блоком управления чтением/записью, выберем микросхему 74LS273N. Микросхема представляет собой восьмиразрядный регистр с умощнёнными выходами для

Рис.4.7. Блок управления чтением/записью.

управления большой ёмкостной или низкоомной нагрузкой и может быть использована в качестве магистрального формирователя (рис. 4.8).

Рис.4.8. Цоколёвка 74LS273.

Базовый элемент микросхемы 74LS273 D-триггер , при подаче положительного перепада на вход С включается обратная связь и регистр запоминает поданную но вход D информацию.

Таблица 4.3.

Режимы работы 74LS273N

Н- высокий логический уровень

L- низкий логический уровень

Х- не используется

Выберем элементы:

- DD14 74LS273N.

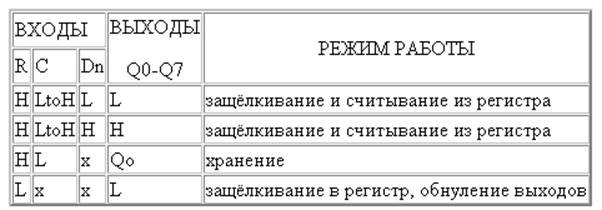

4.5. РАСЧЕТ АЦП и формирователя шины данных.

Наиболее важным блоком осциллографа является аналого-цифровой преобразователь (рис 4.9). Для него выбран АЦП AD7892 производства Analog Devices.

Рис.4.9.Блок АЦП.

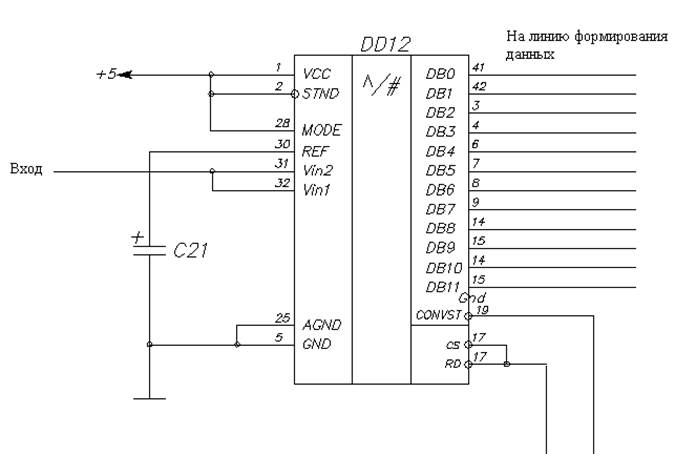

AD7892 – представляет собой высокоскоростной, маломощный, 12-ти битный аналого-цифровой преобразователь с питанием +5 вольт. Его внутренняя структура представлена на рисунке 4.10. Сама микросхема включает в себя 1.47 нс АЦП последовательного приближения, внутренний усилитель, встроенное питание +2.5 В и универсальный интерфейс, которые позволяет реализовать последовательное и параллельное соединение с микропроцессором. Аналоговый вход имеет диапазон ± 10 В и защиту от перенапряжения, что позволяет входному напряжению идти на ±17 В, не повреждая входные порты.

AD7892 может выдавать данные двух типов: отдельное, параллельное, слово на 12 бит или последовательные данные.

Рис.4.10. Внутренняя

структура АЦП AD7892.

Благодаря быстрому времени доступа шины и стандартным входам управления легко реализуется параллельный интерфейс на микропроцессоры и цифровые процессоры сигнала. Высокая скорость последовательного интерфейса позволяет прямую связь с последовательными портами микроконтроллеров и процессорами.

Микросхема может работать как от внешнего , так и внутреннего

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.