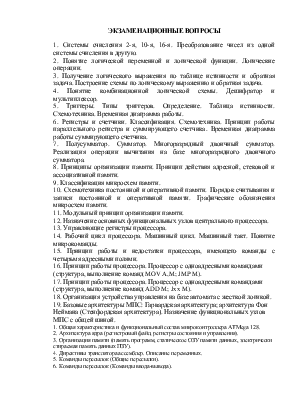

ЭКЗАМЕНАЦИОННЫЕ ВОПРОСЫ

1. Системы счисления 2-я, 10-я, 16-я. Преобразование чисел из одной системы счисления в другую.

2. Понятие логической переменной и логической функции. Логические операции.

3. Получение логического выражения по таблице истинности и обратная задача. Построение схемы по логическому выражению и обратная задача.

4. Понятие комбинационной логической схемы. Дешифратор и мультиплексор.

5. Триггеры. Типы триггеров. Определение. Таблица истинности. Схемотехника. Временная диаграмма работы.

6. Регистры и счетчики. Классификация. Схемотехника. Принцип работы параллельного регистра и суммирующего счетчика. Временная диаграмма работы суммирующего счетчика.

7. Полусумматор. Сумматор. Многоразрядный двоичный сумматор. Реализация операции вычитания на базе многоразрядного двоичного сумматора.

8. Принципы организации памяти. Принцип действия адресной, стековой и ассоциативной памяти.

9. Классификация микросхем памяти.

10. Схемотехника постоянной и оперативной памяти. Порядок считывания и записи постоянной и оперативной памяти. Графические обозначения микросхем памяти.

11. Модульный принцип организации памяти.

12. Назначение основных функциональных узлов центрального процессора.

13. Управляющие регистры процессора.

14. Рабочий цикл процессора. Машинный цикл. Машинный такт. Понятие микрокоманды.

15. Принцип работы и недостатки процессора, имеющего команды с четырьмя адресными полями.

16. Принцип работы процессора. Процессор с одноадресными командами (структура, выполнение команд MOV A,M; JMP M).

17. Принцип работы процессора. Процессор с одноадресными командами (структура, выполнение команд ADD M; Jxx M).

18. Организация устройства управления на базе автомата с жесткой логикой.

19. Базовые архитектуры МПС: Гарвардская архитектура; архитектура Фон Неймана (Стенфордская архитектура). Назначение функциональных узлов МПС с общей шиной.

1. Общая характеристика и функциональный состав микроконтроллера АТМеgа 128.

2. Архитектура ядра (регистровый файл, регистры состояния и управления).

3. Организация памяти (память программ, статическое ОЗУ памяти данных, электрически стираемая память данных ПЗУ).

4. Директивы транслятора ассемблер. Описание переменных.

5. Команды пересылок (Общие пересылки).

6. Команды пересылок (Команды ввода-вывода).

7. Команды пересылок (Обмен со стеком).

8. Команды обработки данных (логические операции).

9. Команды обработки данных (арифметические операции).

10. Команды обработки данных (сдвиги).

11. Команды обработки данных (операции с битами).

12. Команды передачи управления (безусловные переходы).

13. Команды передачи управления (условные переходы).

14. Команды передачи управления (организация подпрограмм).

15. Команды передачи управления (организация прерываний).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.