Линии ввода/вывода используемые приемопередатчиками сведены в таблицу 1.

Выводы, используемые модулями USART:

Таблица 1

|

Название |

Функция |

Линия ввода/вывода |

Модуль USART |

|

RXD0 TXD0 XCK0 |

Прием Передача Синхронизация |

PE0 PE1 PE2 |

USART0 |

|

RXD1 TXD1 XCK1 |

Прием Передача Синхронизация |

PD2 PD3 PD5 |

USART1 |

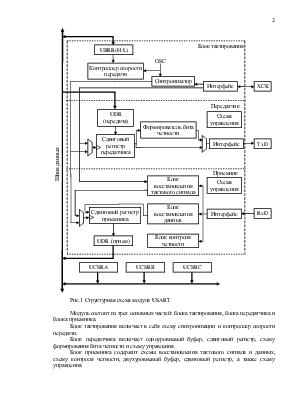

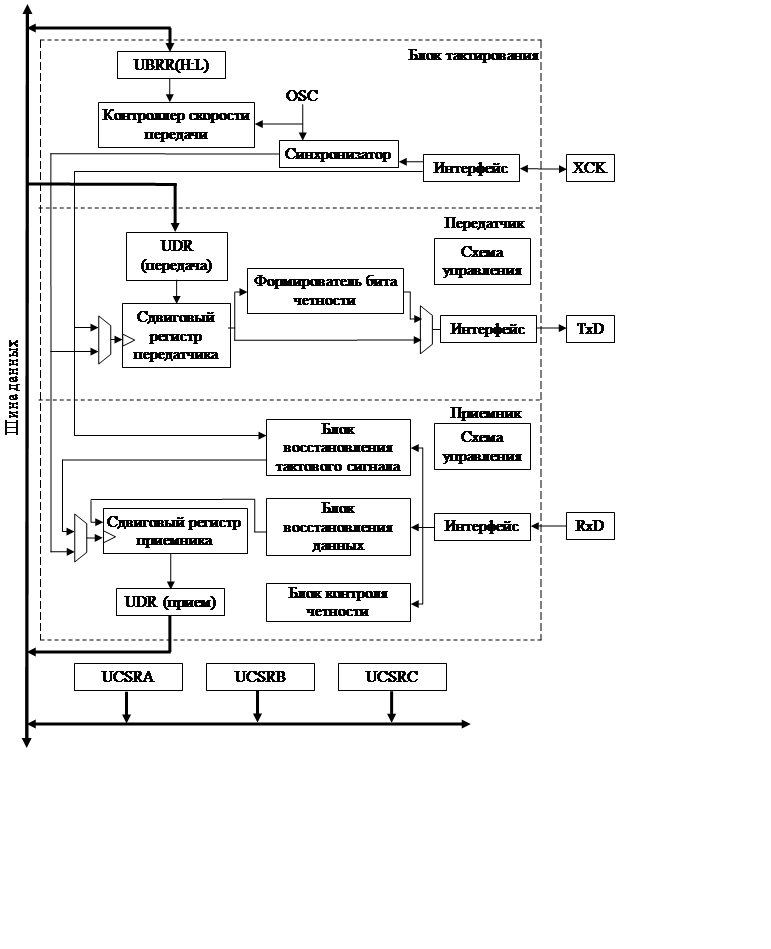

Упрощенная схема одного модуля USART приведена на рисунке 1.

Рис.1 Структурная схема модуля USART

Модуль состоит из трех основных частей: блока тактирования, блока передатчика и блока приемника.

Блок тактирования включает в себя схему синхронизации и контроллер скорости передачи.

Блок передатчика включает одноуровневый буфер, сдвиговый регистр, схему формирования бита четности и схему управления.

Блок приемника содержит схемы восстановления тактового сигнала и данных, схему контроля четности, двухуровневый буфер, сдвиговый регистр, а также схему управления.

Буферные регистры приемника и передатчика располагаются по одному адресу и обозначаются как регистр данных UDRn, где n=0,1. В этом регистре хранятся 8 разрядов принимаемых и передаваемых данных.

2. Регистры состояния и управления

Для управления модулями USART используются три регистра UCSRnA, UCSRnB и UCSRnС.

Формат регистра UCSRnА:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

RXCn |

TXCn |

UDREn |

FЕn |

DORn |

UPEn |

U2Xn |

MPCMn |

UCSRnА |

Разряды регистра UCSRnА:

RXCn – флаг завершения приема. Устанавливается в «1» при наличии непрочитанных данных в регистре UDRn приемника. Сбрасывается аппаратно, после прочтения регистра UDRn.

TXCn – флаг завершения передачи. Устанавливается в «1» после передачи всех разрядов, записанных в UDRn, из сдвигового регистра передатчика. Сбрасывается аппаратно при выполнении подпрограммы обработки прерывания «передача завершена» или программно, записью в него логической единицы.

UDREn – флаг опустошения регистра данных. Устанавливается в «1» после пересылки байта из регистра данных UDRn в сдвиговый регистр передатчика. Сбрасывается аппаратно, при записи байта в регистр UDRn.

FЕn – флаг ошибки кадрирования.

DORn – флаг переполнения.

UPEn – флаг ошибки контроля на четность.

U2Xn – удвоение скорости обмена. Используется только в асинхронном режиме. В синхронном режиме флаг всегда равен 0. Если U2Xn=1, скорость асинхронного обмена по последовательному каналу удваивается.

MPCMn – режим мультипроцессорного обмена.

Формат регистра UCSRnВ:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

RXCIEn |

TXCIEn |

UDRIEn |

RXENn |

TXENn |

UCSZn2 |

RXB8n |

TXB8n |

UCSRnB |

Разряды регистра UCSRnВ:

RXCIEn - разрешение прерывания «прием завершен». Если бит равен «1», то при установке флага RXCn регистра UCSRnА генерируется прерывание «прием завершен» (если в регистре SREG флаг I=1).

TXCIEn – разрешение прерывания «передача завершена». Если разряд равен «1», то при установки флага TXCn регистра UCSRnА генерируется прерывание «передача завершена» (если в SREG флаг I=1).

UDRIEn – разрешение прерывания «регистр данных пуст». Если бит равен «1», то при установки флага UDREn регистра UCSRnA генерируется прерывание «регистр данных пуст» (если в SREG флаг I=1).

RXENn – разрешение передачи (при RXENn=1).

TXENn – разрешение приема (при TXENn=1).

UCSZn2 – формат посылки. Совместно с битами UCSZn1 и UCSZn0 регистра UCSRnС определяет количество бит данных (от 5 до 9) в кадре посылки.

RXB8n – 9-ый разряд принимаемых данных.

TXB8n – 9-ый разряд передаваемых данных.

Формат регистра UCSRnС:

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

-- |

UMSELn |

UPMn1 |

UPMn0 |

USBSn |

UCSZn1 |

UCSZn0 |

UCPOLn |

UCSRnC |

Разряды регистра UCSRnC:

UMSELn – режим работы. 0-асинхронный. 1-синхронный.

UPM – контроль на четность (нечетность).

Таблица 2. Управление контролем четности

|

UPMn1 |

UPMn0 |

Режим |

|

0 |

0 |

Выключен |

|

1 |

0 |

Проверка на четность |

|

1 |

1 |

Проверка на нечетность |

USBSn – количество стоп-битов. «0» – 1 стоп-бит. «1» – 2 стоп-бита.

UCSZn – формат посылок (размер слова).

Таблица 3. Определение размера слова данных

|

Режим |

UCSZn2 |

UCSZn1 |

UCSZn0 |

Размер слова |

|

Асинхронный |

0 1 |

0 0 |

0 0 |

8р 9р |

|

Синхронный |

0 0 0 0 1 |

0 0 1 1 1 |

0 1 0 1 1 |

5р 6р 7р 8р 9р |

UCPOLn – полярность тактового сигнала. Значение разряда определяет фронт синхросигнала XCKn в момент выдачи и считывания данных на выходах модуля. «0» - спадающий фронт, при выдаче и нарастающий, при считывании. «1» – нарастающий фронт, при выдаче и спадающий, при считывании.

3. Скорость приема/передачи

Скорость приема и передачи данных по последовательному каналу задается контроллером скорости передачи, функционирующим как делитель системного тактового сигнала. Коэффициент деления определяется содержимым регистра контроллера UBRR.

Регистр UBRR является 12-разрядным и физически размещается в двух 8-разрядных регистрах ввода/вывода UBRRnH и UBRRnL.

Скорость обмена определяется следующими формулами:

а) асинхронный режим (обычный, V2Xn=0)

BAUD=fCK/(16*( UBRR+1));

б) асинхронный режим (ускоренный, V2Xn=1)

BAUD=fCK/(8*( UBRR+1));

в) синхронный режим ведущего

BAUD=fCK/(2*( UBRR+1));

Пример: рассчитать значение, помещаемое в регистр UBRR, для обычного асинхронного режима обмена, если частота кварцевого резонатора fCK=7,3728 МГц и скорость обмена BAUD=115200 бод.

UBRR = fCK/(16* BAUD) – 1=7372800/(16*115200) – 1=3

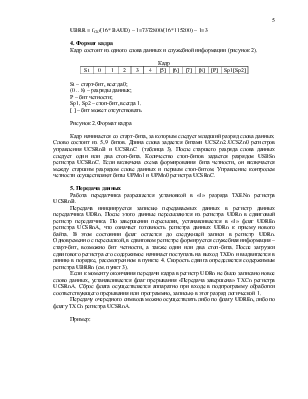

4. Формат кадра

Кадр состоит из одного слова данных и служебной информации (рисунок 2).

|

Кадр |

|||||||||||

|

St |

0 |

1 |

2 |

3 |

4 |

[5] |

[6] |

[7] |

[8] |

[P] |

Sp1[Sp2] |

St – старт-бит, всегда 0;

(0 .. 8) – разряды данных;

Р – бит четности;

Sp1, Sp2 – стоп-бит, всегда 1.

[ ] – бит может отсутствовать

Рисунок 2. Формат кадра

Кадр начинается со старт-бита, за которым следует младший разряд слова данных. Слово состоит из 5..9 битов. Длина слова задается битами UCSZn2..UCSZn0 регистров управления UCSRnB и UCSRnC (таблица 3). После старшего разряда слова данных следует один или два стоп-бита. Количество стоп-битов задается разрядом USBSn регистра UCSRnC. Если включена схема формирования бита четности, он включается между старшим разрядом слове данных и первым стоп-битом. Управление контролем четности осуществляют биты UPMn1 и UPMn0 регистра UCSRnC.

5. Передача данных

Работа передатчика разрешается установкой в «1» разряда TXENn регистра UCSRnB.

Передача инициируется записью передаваемых данных в регистр данных передатчика UDRn. После этого данные пересылаются из регистра UDRn в сдвиговый

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.