Федеральное Агентство по Связи

Сибирский Государственный Университет Телекоммуникаций и Информатики

Кафедра ТЭ

Курсовая работа:

“Разработка цифрового интегрального устройства ”

Выполнил:ст.Гр.Р-51

Лимонов Александр

Проверил: Квашнин

Евгений Фомич

Новосибирск 2007.

1.Введение.

Современный этап развития радиотехники, электронной техники и техники связи характеризуется их взаимным проникновением и широким использованием практически во всех областях науки и техники, а также значительным усложнением требований и задач, решаемых радиоэлектронной аппаратурой.

Интегральная и функциональная микроэлектроника, являются фундаментальной базой развития всех систем радиоэлектронной аппаратуры.

Микроэлектроника – одно из магистральных направлений в радиоэлектронике, и уровень ее развития в значительной степени определяет уровень научно-технического прогресса страны.

Интегральные микросхемы служат элементарной базой практически всех типов радиоаппаратуры.

Потребности обеспечения систем связи, радиолокации, промышленной автоматики, космических исследований, транспортных средств и т. д. интегральными микросхемами высокого качества привели к разработке и выпуску большой номенклатуры ИМС с непрерывно возрастающей степенью интеграции. При этом производная роста сложности ИМС существенно выше аналогичного показателя для аппаратуры.

Совершенствование радиоэлектронной аппаратуры связано с широким использованием элементов микроэлектроники, заменой механических и электромеханических узлов и блоков электронными с комплексной миниатюризацией.

В данной курсовой работе перед нами предстоит задача,

заключающаяся в разработке электрической схемы цифрового устройства, топологии цифрового устройства и расчёте режимов работы цифрового устройства

2. Первая часть.

Разработка электрической схемы цифрового устройства.

2.1 Задание.

Разработать электрическую схему цифрового устройства, выполняющего нижеприведенные функции. При этом нужно соблюдать следующие требования:

· Общая потребляемая мощность устройства не должна превышать указанное в задании значение;

· Время задержки распространения сигнала по самому длинному пути не должно превышать заданное значение;

· Приведены требования к выходным элементам - они должны иметь открытый коллекторный стоковый выход;

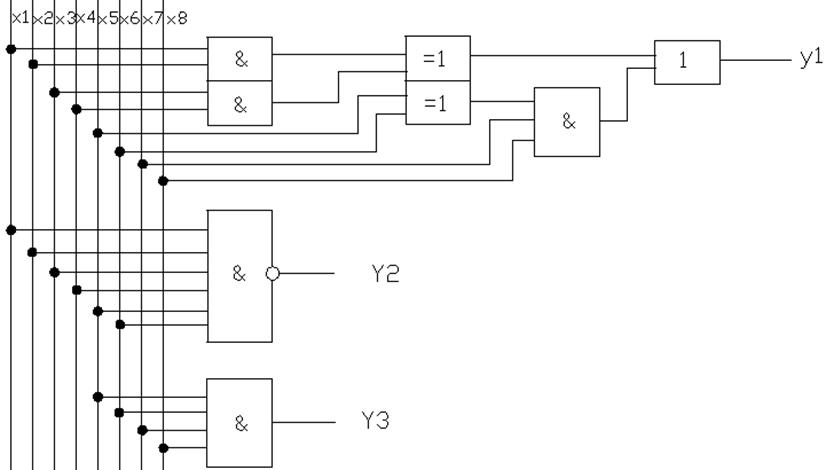

Y1=X1*X2*X3*X4+ X1*X2*X3*X4+(X5*X6*X7+ X5*X6*X7)*X8

Y2= X1*X2*X3+X4*X5*X6

Y3= X5*X6*X7*X8

Рпотр < 70 мВт![]()

![]()

2.2 Упрощаем исходные уравнения (используя законы алгебраической логики).

Первая логическая функция:

![]()

![]()

![]()

![]() Y1=X1*X2*

X3*X4+ X1*X2*X3*X4+(X5*X6*X7+ X5*X6*X7)*X8=

Y1=X1*X2*

X3*X4+ X1*X2*X3*X4+(X5*X6*X7+ X5*X6*X7)*X8=

![]()

![]()

= (X1*X2) + (X3*X4) + (X5 + X6)*X7*X8

Вторая логическая функция:

Y2=X1*X2*X3+X4*X5*X6= X1*X2*X3*X4*X5*X6

Третья логическая функция:

Данная функция не нуждается в упрощении, т.е. её целесообразней оставить такой какая она есть

Y3= X5*X6*X7*X8

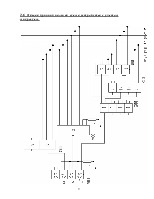

2.3 Общая структурная логическая схема устройства.

Составляя структурная схему, мы используем набор логических элементов, выполняющих элементарные операции, с помощью которых в двоичном коде можно реализовать любую сложную логическую функцию.

Так же нужно обратить внимание на то , что количество логических элементов в схеме должно минимально

2.4 Выбор типа логики

В условии задания оговорено, что:

Рпотр ≤ 70 мВт

tзд.р.ср ≤ 60 нсек

. Если брать серии только ТТЛ и ТТЛШ (даже самые дорогие) , то хотя бы одно из условий не будет выполняться. В другом варианте, если брать только серии логик КМДП, то схема получится менее компактной, так как среди ТТЛ и ТТЛШ есть весьма удобные для данного случая прототипы .Отсюда следует только один выход: использовать часть серий из логики ТТЛ(ТТЛШ) и часть серий логики КМДП. Также следует учитывать, что:

1. В варианте ТТЛ – КМДП для обеспечения необходимого режима по выходу ТТЛ ИМС используются дополнительный резистор с номиналом порядка 1кОм;

2. В варианте КМДП – ТТЛ выход КМДП ИМС непосредственно подсоединяется ко входу ТТЛ ИМС.

2.5 Выбор конкретных ИМС.

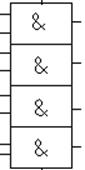

а) DD1: 4 логических элемента «2И»:КР1554ЛИ1

ЕП

= 5 В U1вых ≥ 4.36 В

ЕП

= 5 В U1вых ≥ 4.36 В

Iпотр.ср = 4 мкА t1,0зд.р ≤ 7 нс

I0вых ≤ 24 мА t0,1зд.р ≤ 7.5 нс

I1вых ≤ -24 мА Рпотр.ср. = 20 мкВт

U0вых ≤ 0.32 В tзд.р ср. = 7,25 нс

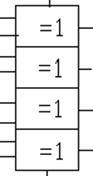

б) DD2: 4 логических элемента «ИСКЛ. ИЛИ»:КР1554ЛП5

ЕП=

5 В U1вых ≥ 4.36 В

ЕП=

5 В U1вых ≥ 4.36 В

Iпотр.ср= 8 мкА t1,0зд.р ≤ 13.5 нс

I0вых ≤ 24 Ма t0,1зд.р ≤ 13.5 нс

I1вых ≤ -24 мА Рпотр.ср.= 40 мкВт

U0вых ≤ 0.32 В tзд.р ср.= 13.5 нс

в) DD3 2 логических элемента «4 И»:КР1533 ЛИ6

I0потр. ≤ 2 мА U0вых ≤ 0.4 В

I0потр. ≤ 2 мА U0вых ≤ 0.4 В

I1потр ≤ 1.1 мА U1вых ≥ 2.5 В

I0вх ≤ -0.1 мА t1,0зд.р ≤ 10 нс

I1вх ≤ 0.02 мА t0,1зд.р ≤ 26 нс

I0вых ≤ 8 мА Рпотр.ср.= 7.75 мВт

I1вых ≤ -0.4 мА tзд.р ср.= 18 нс

г) DD4: логический элемент «8 И-НЕ»: КР1533ЛА2

I0потр. ≤ 0.9 мА U0вых ≤ 0.4 В

I0потр. ≤ 0.9 мА U0вых ≤ 0.4 В

I1потр ≤ 0.31 мА U1вых ≥ 2.5 В

I0вх ≤ -0.1 мА t1,0зд.р ≤ 12 нс

I1вх ≤ 0.02 мА t0,1зд.р ≤ 10 нс

I0вых ≤ 8 мА Рпотр.ср.= 3.025 мВт

I1вых ≤ -0.4 мА tзд.р ср.= 11 нс

д)DD5: 4 логических элемента «2 ИЛИ»:КР1554ЛЛ1

ЕП

= 5 В U1вых ≥ 4.36 В

ЕП

= 5 В U1вых ≥ 4.36 В

Iпотр.ср = 4 мкА t1,0зд.р ≤ 7 нс

I0вых ≤ 24 мА t0,1зд.р ≤ 7.5 нс

I1вых ≤ -24 мА Рпотр.ср. = 20 мкВт

U0вых ≤ 0.32 В tзд.р ср. = 7,25 нс

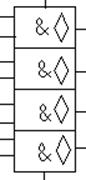

е)DD6 4 логических элемента «2И» с открытым стоковым выходом:КР1564ЛИ2

ЕП

= 5 В U1вых ≥ 4.36 В

ЕП

= 5 В U1вых ≥ 4.36 В

Iпотр.ср = 4 мкА t1,0зд.р ≤ 7 нс

I0вых ≤ 24 мА t0,1зд.р ≤ 7.5 нс

I1вых ≤ -24 мА Рпотр.ср. = 20 мкВт

U0вых ≤ 0.32 В tзд.р ср. = 7,25 нс

2.6 Общая принципиальная схема устройства с учетом микросхем.

Примечания:

1) если часть входов логического элемента используется, а часть

нет, то необходимо на неиспользуемые входы подать постоянный уровень нуля или единицы. В нашем случае нам необходимо получить уровень единицы ,так как уровень нуля исказить значение выходного сигнала, поэтому мы на неиспользуемые входы через резистор(во избежание слишком большого входного тока, и выхода микросхемы из строя) подаём напряжение питания.

2)если все входы какого-либо логического элемента не используются, то их следует заземлить.

2.8 Расчет максимального времени задержки и потребляемой мощности.

Проверим выполнение условий, которые даны в задании:

· Мощность потребляемая всеми логическими элементами равна:

Pпотр.сх=Pпотр DD1+ Pпотр DD2+ Pпотр DD3+ Pпотр DD4+ Pпотр DD5+ Pпотр DD5

Pпотр.сх=0.02+0.04+7.75+3.025+0.02+0.025=10.88 мВт

РПОТР.СХ < РПОТР

10.88мВт<70 мВт

· Время задержки по самому длинному пути равно:

tзд.р.ср.сх= tDD1ср+ tDD2ср+ tDD5ср+tDD6ср=7.25+13.5+7.25+24=52,5 нс

tзд.р.ср.сх <tзд.р.ср

52.5 нс < 60 нс

Все условия , указанные в задании - выполняются, следовательно, серии ИМС выбраны верно.

3. Вторая часть.

Расчет режимов работы электронной схемы цифрового устройства.

3.1. Задание

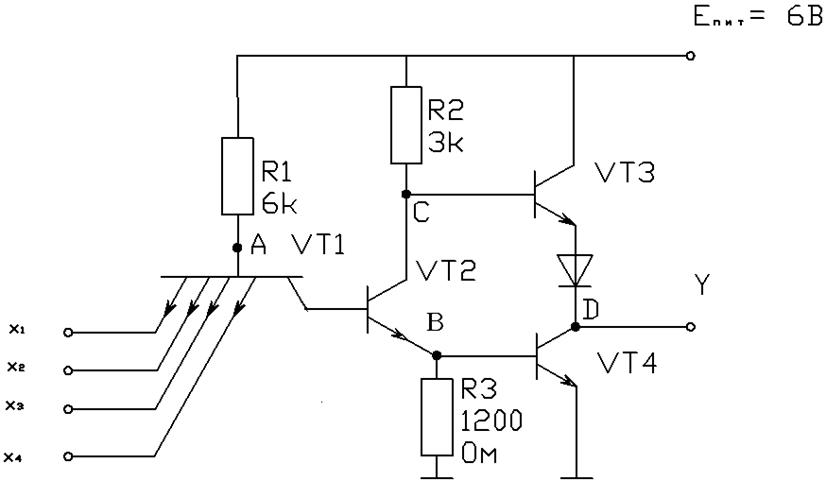

Дана электрическая схема. Необходимо провести расчёт работы данной схемы

Электрическая схема:

Комбинации на входах: 0000

1111

1100

При выполнении расчетов предполагается принять:

· U0вх=0,1В U1вх=3В

· Ток БТ, находящегося в режиме отсечки Iкэо,не более 1мкА;

· Напряжение между коллектором и эмиттером БТ находящегося в режиме насыщения 0,1В;

· Напряжение на переходе коллектор-база БТ при прямом включении 0,7В;

· Напряжение на переходе коллектор-база при прямом включении 0,6В;

· Коэффициент передачи тока БТ при прямом включении ß=50;

· Коэффициент передачи тока БТ в инверсном режиме ßи=0,05.

Т.к. логические элементы обычно работают совместно с подобными

схемами, то при расчете можно значение выходного тока базового

элемента приравнять значению его выходного тока.

Весь расчет основан на оценке потенциалов в узловых точках схемы.

Проанализируем работу схемы при подаче на вход трех различных комбинаций:

Для удобства дальнейших расчетов, первоначально определим

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.