- J-K триггер с логикой на входах J и K. Условное обозначение: КМ555ТВ1

|

Параметр |

Значение параметра |

|

Число выводов |

16 |

|

Средняя потребляемая мощность, Pср |

22мВт |

|

Время задержки выходов от входа CLOCK Выход " Q" от входа "PRESET" Выход "-Q" от входа "PRESET" Выход "-Q" от входа "Clear" Выход " Q" от входа "Clear" Максимальная тактовая частота |

25нс 25нс 40нс 25нс 40 нс 20МГц |

Т.к. в схеме 4 J-K триггера, средняя потребляемая мощность увеличится в 4 раза

- 4 элемента 2И в одном корпусе. Условное обозначение К555ЛИ1

|

Параметр |

Значение параметра |

|

Число выводов |

14 |

|

Средняя потребляемая мощность, Pср Среднее время задержки |

36мВт 24нс |

-4 элемента 2ИЛИ в одном корпусе. Условное обозначение К555ЛЛ1

|

Параметр |

Значение параметра |

|

Число выводов |

14 |

|

Средняя потребляемая мощность, Pср Среднее время задержки |

44мВт 22нс |

-элемент 3И+2ИЛИ. Условное обозначение К555ЛИ4

|

Параметр |

Значение параметра |

|

Число выводов |

14 |

|

Средняя потребляемая мощность, Pср Среднее время задержки |

18мВт 15нс |

Температурный диапазон работоспособности микросхем КМ555 -45..+85 градусов по Цельсию.

Средняя потребляемая мощность схемы будет рассчитываться следующим образом:

P = 4*22+36+44+18 = 186 мВт, что удовлетворяет требованиям задания.

Входы микросхем серий КМ555 можно подключать к источнику питания +5В непосредственно, без предварительной нагрузки.

Время наработки на отказ микросхем серии КМ555 порядка 15 лет, что составляет примерно 131400 часов.

Элементы КМ555 серии выдерживают синусоидальную вибрации до 2кГц, перегрузки всякого рода до 15g включительно, одиночный удар до 10g.

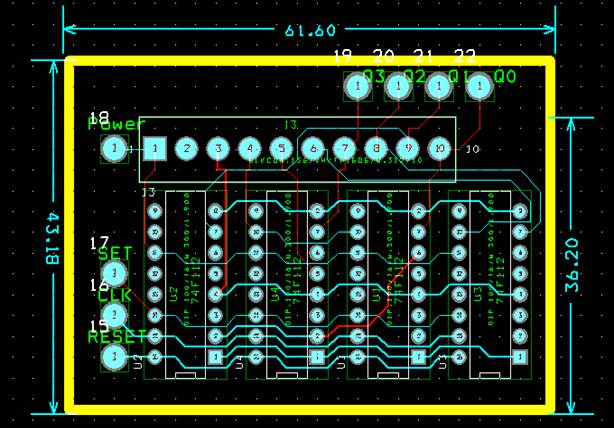

Используя логику на входах J и K триггеров, и, объединив элементы К555ЛИ4, К555ЛЛ1 и К555ЛИ1, можно собрать следующую печатную плату, используя пакет Layout Plus семейства OrCad:

Рис.5 Печатная плата

Размеры платы проставлены в миллиметрах.

Печатная плата разведена в 2 слоя, что целесообразнее, чем в 1 слой с точки зрения количества дорожек, при этом данное решение не намного дороже. Предусмотрены установка начального состояния сигналами SET и RESET, и выходы Q-сигналов.

8. Оценка степени выполнения задания

Был произведен синтез 4-х разрядного синхронного счётчика на JK триггерах. Счётчик удовлетворяет всем требованиям, перечисленным в задании.

Список литературы:

1. Цифровые устройства. Конспект лекций Астанина Л.Ю.

2. Популярные цифровые микросхемы. Справочник. Шило В.Л. Радио и связь, 1989

3. Материалы сайта http://www.rgost.ru

4. Материалы сайта http://lib.qrz.ru/

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.