|

|

|

||||

|

X |

1 |

O |

X |

||

|

X |

O |

X |

X |

||

|

|

X |

X |

1 |

X |

|

|

X |

O |

O |

X |

|

|

|

|

|

|

|

||||

|

1 |

1 |

1 |

1 |

||

|

X |

1 |

X |

X |

||

|

|

X |

X |

X |

X |

|

|

X |

X |

X |

X |

|

|

|

|

|

|

|

||||

|

X |

X |

X |

X |

||

|

X |

X |

X |

X |

||

|

|

X |

X |

1 |

X |

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

||||

|

O |

O |

O |

O |

||

|

X |

X |

X |

X |

||

|

|

X |

X |

X |

X |

|

|

O |

O |

1 |

O |

|

|

|

|

|

|

|

||||

|

X |

X |

X |

X |

||

|

X |

O |

X |

X |

||

|

|

X |

X |

1 |

X |

|

|

X |

X |

X |

X |

|

|

|

|

После процедуры склеивания получим следующие логические уравнения для входов триггеров:

|

|

|

|

|

|

|

|

|

|

|

|

Исходя из полученных уравнений видно, что для реализации схемы нам понадобится:

1. 4 JK триггера,

2. 5 элементов «И»

3. 3 элемента «ИЛИ»

Принимая во внимание техническое задание и условия эксплуатации, выберем следующие элементы:

1. В качестве JK триггера будем использовать микросхему К561ТВ1

2. В качестве элемента «И» будем использовать микросхему КР1561ЛИ2

3. В качестве элемента «ИЛИ» будем использовать микросхему К561ЛП2

Для микросхем были выбраны серии КР1561 и К561 т.к. эти серии одни из немногих подходит нам по времени наработки на отказ. Далее выбор исходил из минимальности потребляемой мощности, и минимального времени задержки.

Остальные технические и эксплуатационные требования к элементам так же были выполнены при выборе данных элементов.

Вот некоторые из параметров микросхем:

К561ТВ1

|

Iпот, мкА |

|

|

|

|

Uип, В |

В |

В |

|

280 |

0.72 |

0.33 |

590 |

770 |

3-15 |

0.8 |

4.2 |

Микросхемы КР1561ЛИ2 и К561ЛП2 имеют потребляемую мощность

5 мВт и время задержки 10 нс.

После получения логических уравнений и выбора элементов, остаётся только соединить эти элементы, придерживаясь, правил.

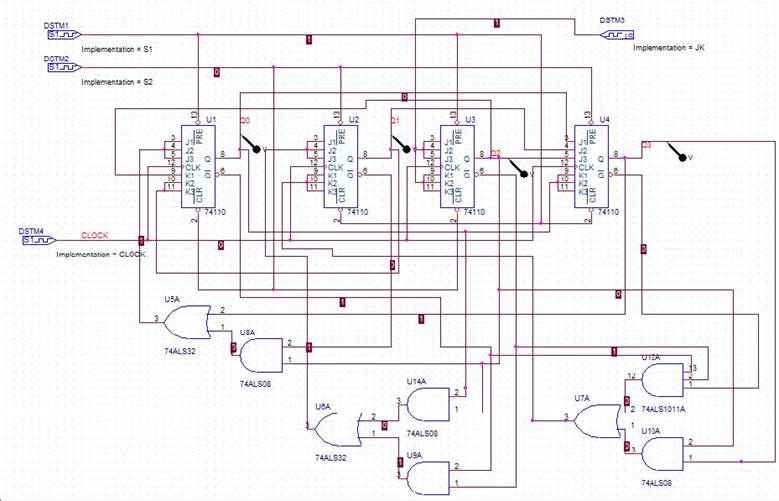

Рис.1 Принципиальная электрическая схема

Устройство имеет 4 выхода ![]() на

которые в соответствии с заданным порядком счёта поступает двоичный код.

Цифровые генераторы DSTM1 и DSTM2

обеспечивают задание начального значения счётчика. Генератор DSTM4

посылает синхроимпульсы на заданные входы счётчиков.

на

которые в соответствии с заданным порядком счёта поступает двоичный код.

Цифровые генераторы DSTM1 и DSTM2

обеспечивают задание начального значения счётчика. Генератор DSTM4

посылает синхроимпульсы на заданные входы счётчиков.

Моделирование выполняется в САПР OrCAD. При подаче на входы CLOCK синхроимпульсов, счётчик должен переключаться в соответствии с заданным порядком счёта. В результате моделирования получим:

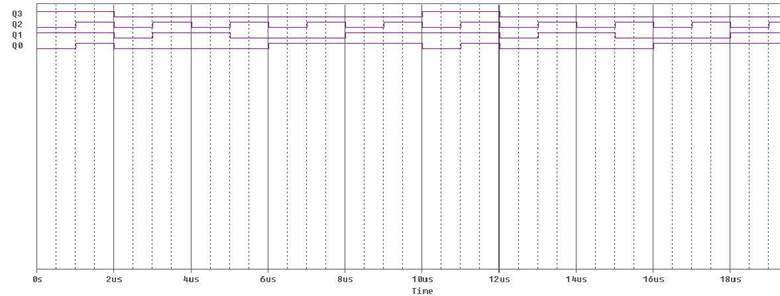

Рис.2 Временные диаграмма работы счётчика

Из временных диаграмм видно, что счётчик по отрицательному фронту синхроимпульсов, переключается в соответствии с заданным порядком счёта. Начальное значение 1010 установлено так же в соответствии с заданием.

Максимальная задержка будет при

прохождении сигнала к входу ![]() . Сигнал

проходит последовательно через элементы «И» , затем через «ИЛИ». Учитывая

выбранные элементы, максимальное время задержки будет 700 нс.

. Сигнал

проходит последовательно через элементы «И» , затем через «ИЛИ». Учитывая

выбранные элементы, максимальное время задержки будет 700 нс.

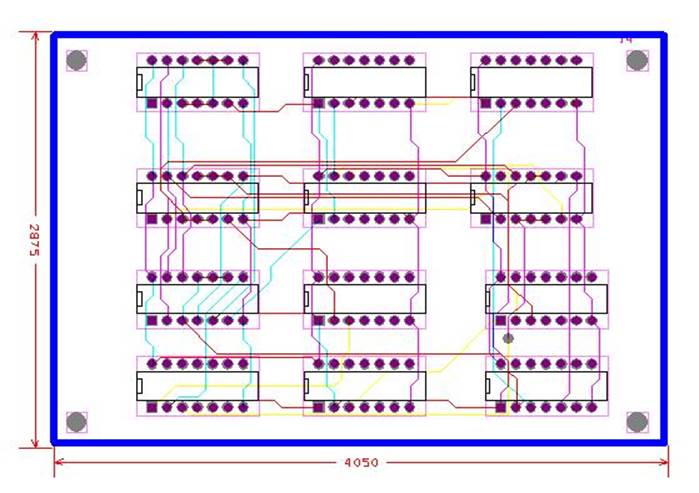

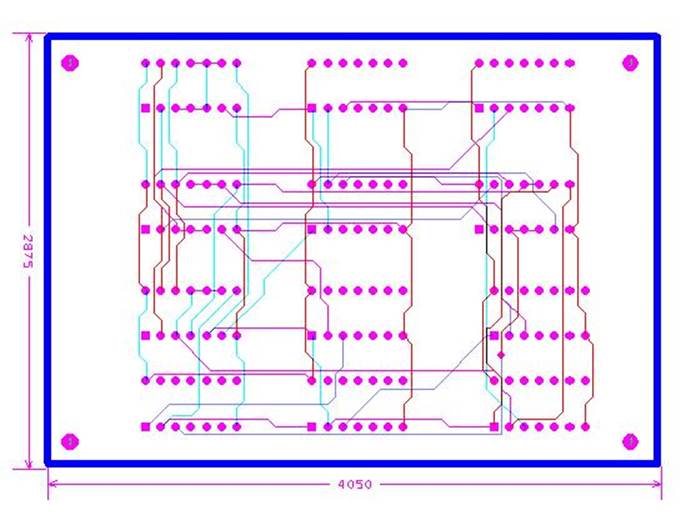

Печатная плата будет конструироваться в OrCAD Layout. Выберем однослойную печатную плату, для простоты конструирования и производства.

Рис. 3 Сборочный чертёж печатного узла

Рис. 4 Чертёж печатной платы

В результате данной работы был спроектирован 4-х разрядный синхронный счётчик с порядком счёта A-F-0-6-2-4-1-5-3-7. Была составлена принципиальная электрическая схема, затем проведено моделирование работы счётчика в САПР OrCAD. Результаты моделирования полностью совпадают с теоретическими результатами. Для данного устройства были подобраны реальные элементы, соответствующие требованиям технического задания, а так же спроектирована печатная плата.

1. Музыченко О.Н. Проектирование цифровых устройств. БГТУ, 1998.

2. Справочник по интегральным микросхемам. Под ред. Тарабрина Б.В.- М.:Энергия, 1981.

3. Петров Ю.В. САПР Orcad ч.3-я,БГТУ,2007.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.