наглядности будем полагать, что пустые ячейки в картах Карно являются неопределёнными.

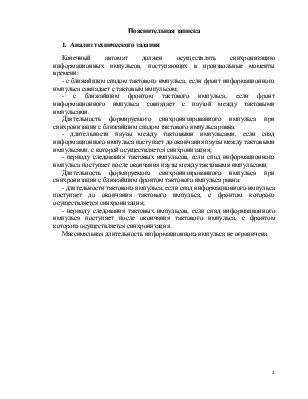

6. Формирование функций выходов и функций возбуждения памяти автомата.

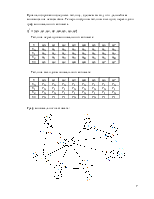

![]()

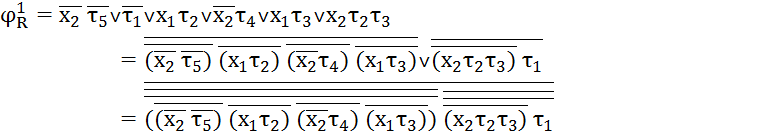

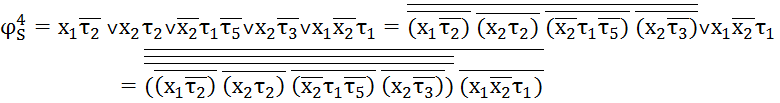

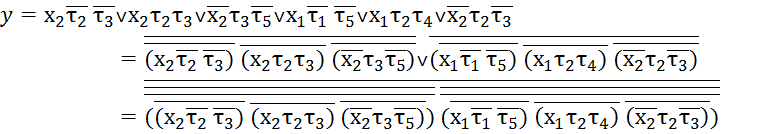

![]() Функция выходов:

Функция выходов:

|

|

|

|

|

|

|

|

1 |

||||||||

|

1 |

0 |

1 |

0 |

0 |

|

||||||||||

|

|

1 |

|

1 |

0 |

0 |

|

1 |

||||||||

|

|

0 |

|

0 |

|

|

1 |

|||||||||

|

0 |

|

0 |

1 |

||||||||||||

|

0 |

1 |

0 |

0 |

1 |

|

||||||||||

|

|

1 |

|

|

1 |

0 |

|

0 |

||||||||

|

1 |

0 |

0 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

В качестве элементов памяти возьмём RS-триггеры.

Функции выходов RS-триггеров:

|

X |

|

||

|

S |

R |

|

|

|

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

0 |

0 |

* |

* |

|

|

|

|

|

0 |

1 - |

0 |

|

0 |

01 |

1 |

|

1 |

10 |

0 |

|

1 |

- 1 |

1 |

Таблица формирования функций возбуждения элементов памяти автомата:

|

X |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

10 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

||||||||

|

01 |

1- |

10 |

-1 |

10 |

-1 |

1- |

1- |

-1 |

1- |

01 |

1- |

01 |

1- |

1- |

-1 |

1- |

-1 |

1- |

1- |

-1 |

1- |

-1 |

1- |

-1 |

01 |

-1 |

1- |

01 |

-1 |

-1 |

-1 |

1- |

-1 |

-1 |

-1 |

10 |

-1 |

1- |

-1 |

|||||||||

|

11 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

||||||||

|

1- |

01 |

10 |

10 |

-1 |

10 |

1- |

1- |

10 |

1- |

1- |

1- |

1- |

1- |

1- |

-1 |

1- |

-1 |

1- |

01 |

-1 |

1- |

-1 |

1- |

-1 |

1- |

-1 |

1- |

1- |

-1 |

-1 |

-1 |

01 |

10 |

-1 |

-1 |

-1 |

-1 |

1- |

-1 |

|||||||||

|

01 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

||||||||

|

1- |

1- |

-1 |

-1 |

-1 |

10 |

1- |

1- |

10 |

1- |

1- |

1- |

1- |

1- |

1- |

10 |

1- |

-1 |

01 |

01 |

10 |

1- |

-1 |

01 |

-1 |

1- |

-1 |

1- |

1- |

-1 |

10 |

10 |

01 |

-1 |

-1 |

-1 |

-1 |

-1 |

1- |

-1 |

|||||||||

|

00 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

||||||||

|

1- |

1- |

-1 |

-1 |

-1 |

-1 |

1- |

1- |

-1 |

1- |

1- |

1- |

01 |

01 |

01 |

-1 |

1- |

-1 |

1- |

1- |

10 |

1- |

-1 |

01 |

-1 |

01 |

-1 |

1- |

01 |

-1 |

-1 |

-1 |

1- |

-1 |

-1 |

10 |

10 |

-1 |

01 |

-1 |

|||||||||

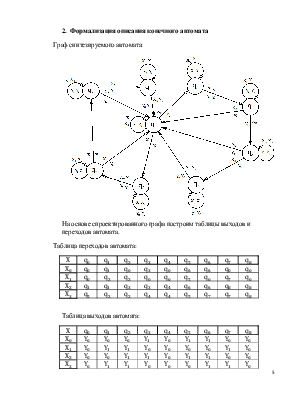

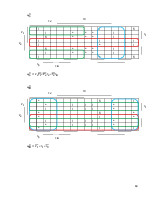

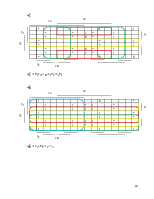

7. Минимизация функции выходов и функций возбуждения памяти автомата, отображение результатов на картах Карно.

![]()

![]()

|

|

0 |

0 |

0 |

||||||||||||

|

|

* |

* |

* |

* |

* |

|

|||||||||

|

|

* |

* |

* |

* |

1 |

||||||||||

|

|

1 |

1 |

1 |

||||||||||||

|

1 |

|

1 |

1 |

||||||||||||

|

|

1 |

* |

1 |

1 |

1 |

|

|||||||||

|

* |

1 |

* |

1 |

* |

|||||||||||

|

0 |

1 |

1 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|||||

|

|

|

|

|

|

1 |

|

|||||||||

|

1 |

1 |

1 |

1 |

1 |

|

||||||||||

|

|

1 |

|

1 |

1 |

1 |

0 |

|||||||||

|

|

* |

* |

* |

||||||||||||

|

* |

* |

* |

|||||||||||||

|

|

0 |

|

1 |

|

0 |

|

|

0 |

|

||||||

|

|

1 |

0 |

1 |

0 |

1 |

|

|||||||||

|

1 |

* |

* |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

* |

1 |

|

1 |

|||||||||||

|

|

* |

1 |

1 |

1 |

1 |

|

|||||||||

|

|

* |

* |

1 |

1 |

1 |

||||||||||

|

|

* |

0 |

1 |

||||||||||||

|

|

* |

1 |

1 |

||||||||||||

|

|

1 |

* |

1 |

1 |

1 |

|

|||||||||

|

|

* |

1 |

* |

1 |

1 |

||||||||||

|

* |

1 |

1 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

1 |

* |

|

* |

|||||||||||

|

1 |

0 |

* |

* |

* |

|

||||||||||

|

|

1 |

|

1 |

* |

* |

* |

|||||||||

|

|

1 |

1 |

* |

||||||||||||

|

1 |

* |

* |

|||||||||||||

|

0 |

1 |

* |

* |

* |

|

||||||||||

|

|

1 |

0 |

* |

* |

|

||||||||||

|

1 |

* |

* |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

1 |

|

1 |

0 |

|||||||||||

|

1 |

* |

* |

* |

1 |

|

||||||||||

|

|

0 |

* |

* |

* |

1 |

||||||||||

|

|

1 |

1 |

1 |

||||||||||||

|

1 |

* |

1 |

|||||||||||||

|

|

0 |

* |

* |

* |

1 |

|

|||||||||

|

1 |

* |

* |

* |

1 |

|||||||||||

|

1 |

* |

0 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|||||

|

|

* |

0 |

|

1 |

|||||||||||

|

* |

1 |

1 |

1 |

* |

|

||||||||||

|

|

1 |

1 |

1 |

1 |

* |

||||||||||

|

|

* |

0 |

* |

||||||||||||

|

* |

1 |

* |

|||||||||||||

|

|

1 |

1 |

1 |

1 |

* |

|

|||||||||

|

* |

1 |

1 |

1 |

* |

|||||||||||

|

* |

1 |

1 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

0 |

|

* |

1 |

|||||||||||

|

|

* |

|

1 |

|

1 |

1 |

|

* |

|

||||||

|

|

1 |

1 |

1 |

1 |

|

1 |

|||||||||

|

|

1 |

1 |

1 |

||||||||||||

|

1 |

* |

1 |

|||||||||||||

|

* |

1 |

0 |

0 |

1 |

|

||||||||||

|

|

* |

|

0 |

|

1 |

0 |

|

* |

|

||||||

|

0 |

* |

0 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

1 |

1 |

* |

||||||||||||

|

1 |

* |

* |

* |

1 |

|

||||||||||

|

|

0 |

* |

* |

* |

0 |

||||||||||

|

|

* |

0 |

* |

||||||||||||

|

|

* |

|

1 |

* |

|||||||||||

|

1 |

* |

1 |

1 |

0 |

|

||||||||||

|

|

1 |

1 |

* |

1 |

1 |

||||||||||

|

1 |

1 |

1 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

* |

|

|

|

1 |

1 |

|||||||||

|

* |

* |

1 |

* |

1 |

|

||||||||||

|

|

* |

* |

0 |

* |

1 |

||||||||||

|

|

* |

* |

1 |

||||||||||||

|

* |

* |

1 |

|||||||||||||

|

* |

* |

0 |

* |

1 |

|

||||||||||

|

* |

|

* |

1 |

* |

1 |

||||||||||

|

* |

* |

0 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

1 |

0 |

* |

||||||||||||

|

|

1 |

1 |

* |

1 |

* |

|

|||||||||

|

|

1 |

1 |

1 |

1 |

* |

||||||||||

|

|

1 |

1 |

* |

||||||||||||

|

|

1 |

1 |

* |

||||||||||||

|

|

1 |

1 |

1 |

1 |

* |

|

|||||||||

|

1 |

1 |

* |

1 |

* |

|||||||||||

|

1 |

1 |

1 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

8. Составление логической схемы устройства.

Логическая схема устройства приведена в Приложении №1.

9. Выбор метода обеспечения контролепригодности и преобразование схемы устройства.

Для повышения контролепригодности разрабатываемого устройства можно предусмотреть ряд мер:

1) Обеспечение простоты начальной установки элементов памяти. В схеме должна обеспечиваться возможность установки всех элементов в начальное состояние.

2) Улучшение характеристик наблюдаемости можно достичь за счет обеспечения доступа к ключевым точкам схемы.

Преобразованная логическая схема с учётом

контролепригодности представлена в Приложении №2.

10. Выбор элементной базы.

Основные параметры типовых ИС:

|

Техно логия |

Тип |

Серия |

Параметр |

|||

|

Рпот, мВт |

tр. тип, нс |

tр. макс, нс |

Эпот., пДж |

|||

|

Б и п о л я р н ы Е |

ТТЛ (Si) быстродействующие |

130 К131 |

22 22 |

6 6 |

10 10 |

132 132 |

|

ТТЛ (Si) Стандартные |

К133 КМ133 К155 КМ155 |

10 10 10 10 |

10 10 10 10 |

22 22 22 22 |

100 100 100 100 |

|

|

ТТЛ (Si) Маломощные |

134 |

1 |

33 |

100 |

33 |

|

|

ТТЛШ (Si) быстродействующие |

530 КР531 КМ531 |

19 19 19 |

3 3 3 |

5 5 5 |

57 57 57 |

|

|

ТТЛШ (Si) маломощные |

533 К555 КМ555 |

2 2 2 |

9,5 9,5 9,5 |

20 20 20 |

19 19 19 |

|

|

ТТЛШ (Si) быстродействующие усовершенствованные |

1531 КР1531 |

4 4 |

3 2 |

6 3,9 |

12 8 |

|

|

ТТЛШ (Si) маломощные усовершенствованные |

КР1533 |

1 |

4 |

11 |

4 |

|

|

ЭСЛ (Si) |

100 К500 К1500 |

25 25 40 |

2 2 0,75 |

2,9 2,9 1 |

50 50 30 |

|

|

Уни по ляр ные |

КМОП (Si) |

К561 564 1564 КР1554 |

0,0025 на 1 МГц |

45 45 10 3,5 |

200 200 45 17 |

0,1 0,1 0,025 0,008 |

|

НОПТШ (GaAs) |

К6500 |

3..6 |

0,1 |

0,42 |

0,3..0,6 |

|

![]() .-

средняя потребляемая мощность.

.-

средняя потребляемая мощность.

![]() .-

время задержки распространения сигнала типовое, максимальное.

.-

время задержки распространения сигнала типовое, максимальное.

![]() - потребление энергии на один бит

информации (энергия переключения).

- потребление энергии на один бит

информации (энергия переключения).

В соответствии с вариантом рассчитываем параметры:

P = 132 мВт

f=0,85 МГц tпер = 1/8f = 147 нс

В соответствии с логической схемой допустимая глубина схемы должна быть не менее 11, а сложность – 67.

|

Технология |

Тип |

Серия |

Параметры |

|

|

Глубина |

Сложность |

|||

|

Биполярные |

ТТЛ (Si) быстродействующие |

130 К131 |

14 |

6 |

|

ТТЛ (Si) Стандартные |

К133 КМ133 К155 КМ155 |

6 |

13 |

|

|

ТТЛ (Si) Маломощные |

134 |

1 |

132 |

|

|

ТТЛШ (Si) быстродействующие |

530 КР531 КМ531 |

29 |

6 |

|

|

ТТЛШ (Si) маломощные |

533 К555 КМ555 |

7 |

66 |

|

|

ТТЛШ (Si) быстродействующие усовершенствованные |

1531 КР1531 |

24 37 |

33 |

|

|

ТТЛШ (Si) маломощные усовершенствованные |

КР1533 |

13 |

132 |

|

|

ЭСЛ (Si) |

100 К500 К1500 |

50 50 148 |

5 5 3 |

|

|

Униполярные |

КМОП (Si) |

К561 564 1564 КР1554 |

- - 7 20 |

132 |

|

НОПТШ (GaAs) |

К6500 |

345 |

22..44 |

|

Допустимые значения внешних воздействующих факторов:

|

Наименование |

Значение |

|

Синусоидальная вибрация: -диапазон, частот, Гц -амплитуда ускорения, м/с2 |

10-500 100 |

|

Механический удар одиночного действия: -пиковое ударное ускорение, м/с2 -длительность действия ударного ускорения, мкс |

100 0.1-1.0 |

|

Механический удар многократного действия: -пиковое ударное ускорение, м/с2 -длительность действия ударного ускорения, мкс |

100 1-5 |

|

Линейное ускорение, м/с2 |

50 |

|

Пониженная температура среды, 0С: -рабочая -предельная |

-10 -60 |

|

Повышенная температура среды, 0С: -рабочая -предельная |

40 55 |

|

Изменения температуры среды, 0С |

от -60 до 55 |

Характеристики надежности и сохраняемости ИС:

|

Серия ИС |

Наработка на отказ, час |

Срок сохраняемости, лет |

|

КР1533 |

50000 |

15 |

Данная серия удовлетворяет техническому заданию.

11. Преобразование схемы устройства с учетом выбранной элементной базы.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

12. Разработка принципиальной схемы устройства.

|

Тип ЛЭ |

Количество ЛЭ |

Тип ИС |

Кол-во ИС |

Число неиспользуемых ЛЭ |

Объем оборудования |

|

НЕ |

8 |

КР1533ЛН1 |

2 |

4 |

19 |

|

2 И-НЕ |

28 |

КР1533ЛА3 |

7 |

0 |

|

|

3 И-НЕ |

20 |

КР1533ЛА4 |

7 |

1 |

|

|

4 И-НЕ |

6 |

КР1533ЛА1 |

3 |

0 |

Чтобы исключить низкочастотные помехи, на печатных платах вблизи разъёма устанавливают развязывающие конденсаторы. Для ТТЛ ИС их ёмкость обычно выбирается из расчёта не менее 0.1 мкФ на одну ИС.

Для исключения ВЧ помех, развязывающие конденсаторы рекомендуется размещать по площади печатной платы из расчёта один конденсатор на группу не более чем из 10 ИС. Для ТТЛ ИС их ёмкость обычно выбирается из расчёта не менее 0.002 мкФ на одну ИС.

Выберем для установки на плате один конденсатор типа КМ-6-Н90-2.0мкФ и два конденсатора типа КМ-6-Н50-0.1мкФ.

13. Расчет основных показателей устройства.

|

Обозначение микросхемы |

Функциональное назначение |

Число выводов корпуса |

Потребляемая мощность мВт |

Макс. усредн. время задержки, нс |

Кол-во |

|

КР1533ЛА3 |

28 элемента 2И-НЕ |

14 |

4 |

9.5 |

7 |

|

КР1533ЛА4 |

20 элемента 3И-НЕ |

14 |

6 |

14.5 |

7 |

|

КР1533ЛА1 |

6 элемента 4И-НЕ |

14 |

10 |

4 |

3 |

|

КР1533ЛН1 |

8 элементов НЕ |

14 |

8 |

9.5 |

2 |

Оценим быстродействие полученной схемы. Для этого рассмотрим путь прохождения сигнала от входа к выходу максимальной глубины:

НЕ→2И-НЕ→4И-НЕ→ НЕ →2И-НЕ→ТР1(2И-НЕ + 3И-НЕ) →3И-НЕ→3И-НЕ→НЕ→2И-НЕ

Таким образом, t.з=9,5+9,5+4+(9,5+14,5)+14,5+14,5+9,5+9,5=95 нс

Максимальная тактовая частота синтезированной схемы равна 1.05МГц, что соответствует требованиям технического задания.

Максимальная потребляемая схемой мощность определяется исходя из характеристик ИС и вариантов их коммутации. Вычислим потребляемую схемой мощность как сумму произведений потребляемых микросхемами мощностей на количество микросхем:

Pмакс= 7*4мВт(КР1533ЛА3)+ 7*6мВт(КР1533ЛА4)+ 2*10мВт (КР1533ЛН1)+ 3*8мВт(КР1533ЛА1)= 114 мВт.

Технические характеристики серии КР1533:

- диапазон рабочих температур -100 С до +700 С ;

-f тактовых импульсов до 70 МГц

Элементы Серии КР1533 слабо зависит от t и f.

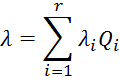

Интенсивность отказов устройства, содержащего разнотипные элементы, определяется следующим соотношением:

Среднее время наработки на отказ устройства составляет:

![]()

Перечень комплектующих элементов устройства и значений интенсивности их отказов:

|

№ |

Тип элемента |

Число элементов Q |

|

Q*λ, |

|

1 |

КР1533ЛА1 КР1533ЛА3 КР1533ЛА4 КР1533ЛН1 |

3 7 7 2 |

0.017*10-6 |

0.051*10-6 0.119*10-6 0.119*10-6 0.034*10-6 |

|

2 |

Паяные соединения |

240 |

10-9 |

240*10-9 |

|

3 |

Конденсаторы |

3 |

0.004*10-6 |

0.012*10-6 |

|

4 |

Вилка разъема |

1 |

0.011*10-6 |

0.011*10-6 |

|

Суммарная интенсивность отказов |

0.586*10-6 |

|||

Время наработки на отказ составит:

![]() часа.

часа.

14. Моделирование работы устройства и составление временной диаграммы его работы, анализ правильности функционирования.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.