Министерство образования Республики Беларусь

Учреждение образования

“Гомельский государственный университетим. Ф. Скорины”

Физический факультет

Кафедра общей физики

Отчет о лабораторной работе

«Моделирование работы дешифраторов

в программе Electronics WorkBench»

|

Выполнил: студент группы ФТТ - 42 |

Гордунов Д.С. |

|

Проверил: |

Грищенко В.В. |

Гомель 2013

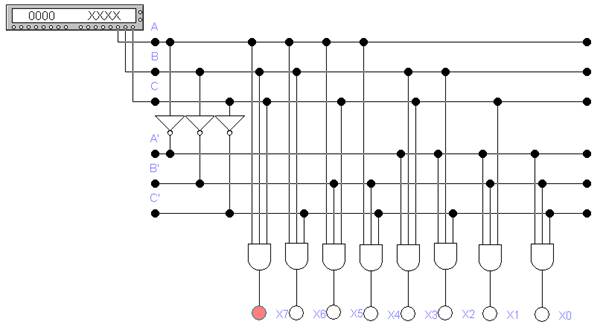

Задание №1. Собрать схему дешифратора из двоичного кода в восьмеричный код, используя логические схемы " И ", заполнить таблицу истинности.

|

ост |

А |

В |

С |

X0 |

X1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

Функция |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Х0 = |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Х1 = |

|

2 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Х2 = |

|

3 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

Х3 = |

|

4 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

Х4 = |

|

5 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Х5 = |

|

6 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

Х6 = |

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Х7 = |

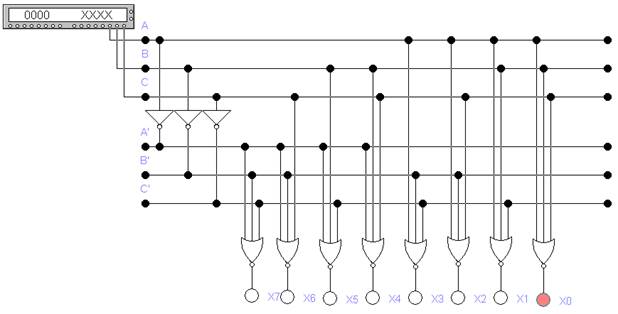

Задание №2. Собрать схему дешифратора из двоичного в восьмеричный код, используя схемы " ИЛИ-НЕ ", и заполнить таблицу истинности.

|

ост |

А |

В |

С |

X0 |

X1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

Функция |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Х0 = |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Х1 = |

|

2 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Х2 = |

|

3 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

Х3 = |

|

4 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

Х4 = |

|

5 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Х5 = |

|

6 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

Х6 = |

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Х7 = |

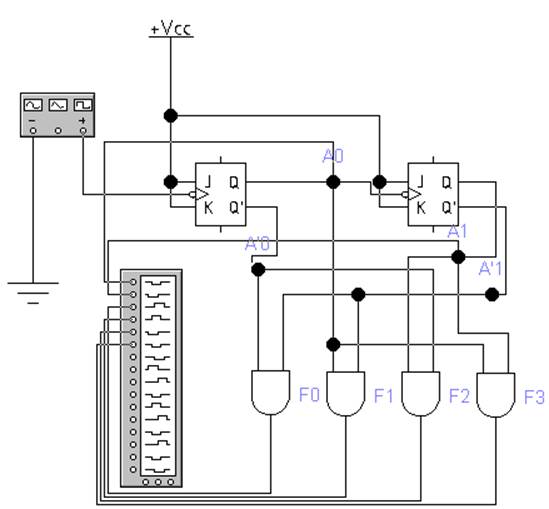

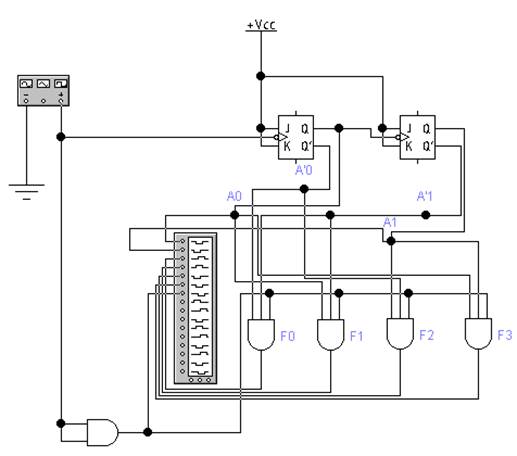

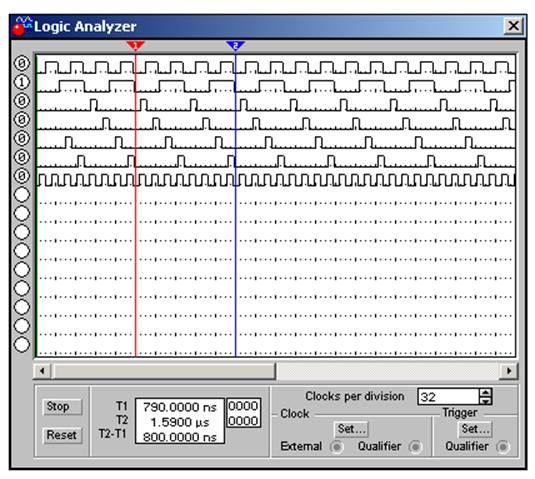

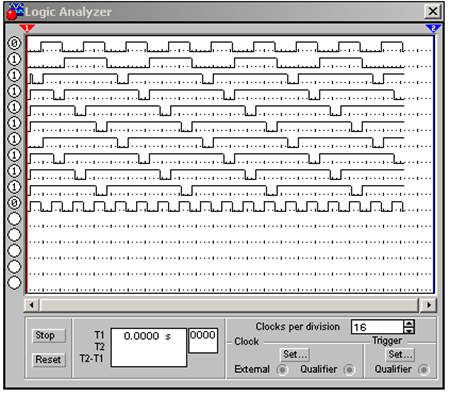

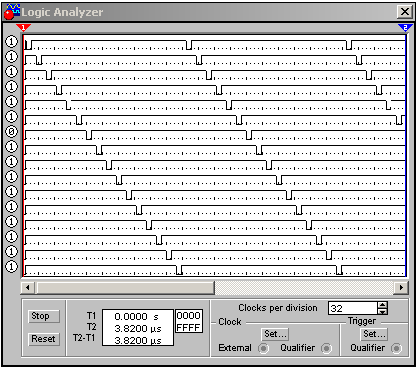

Задание №3. Собрать дешифратор без стробирования, подать на входы сигналы с выходов счетчика (в качестве триггеров использовать JK-тригеры в библиотеке элементов (JK Flip-Flop with Active High Asynch Inputs)). На функциональном генераторе выставить импульсный режим, частота 10 МГц, амплитуда 10В.

Величина возникающей помехи во временной диаграмме составляет 10 (нс).

При

рассмотрении свойств J-K-триггера была

определена строка, которая содержит заданное время задержки срабатывания

устройства. Оно составляет порядка 1![]() 10-8

(с) = 10 (нс).

10-8

(с) = 10 (нс).

|

A1 |

A0 |

F3 |

F2 |

F1 |

F0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

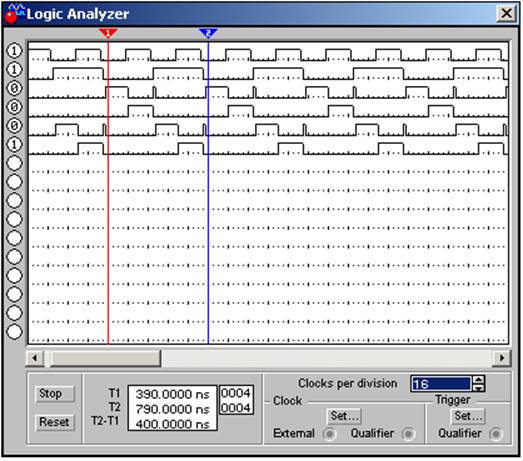

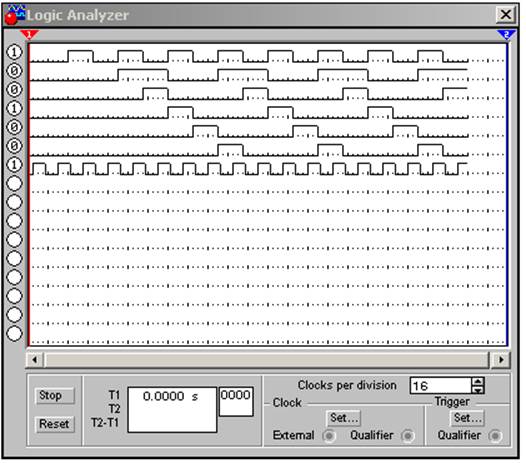

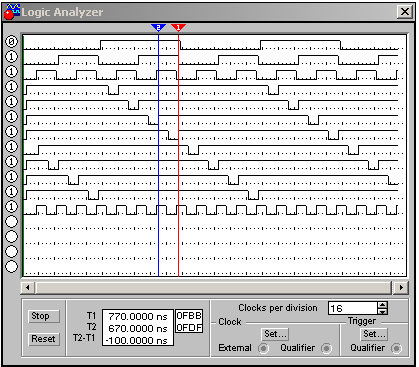

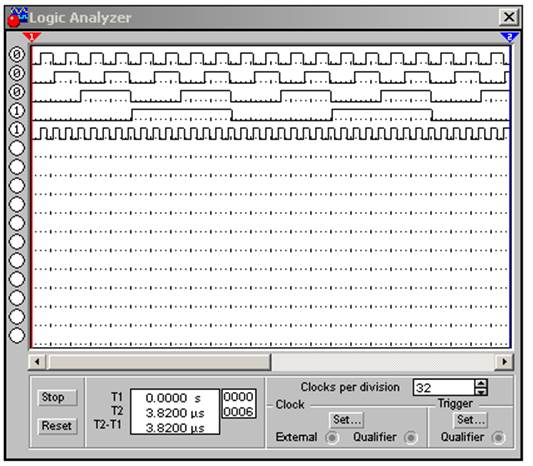

Задание №4. Собрать дешифратор со стробированием.

Таблица истинности.

|

A0 |

A1 |

F0 |

F1 |

F2 |

F3 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

Изменяя время задержки на логических элементах, мне удалось установить необходимое время задержки для устранения помех сигнала на выходе дешифратора, данное значение составило 100 (нс). Представленная ниже временная диаграмма является непосредственно тому подтверждением:

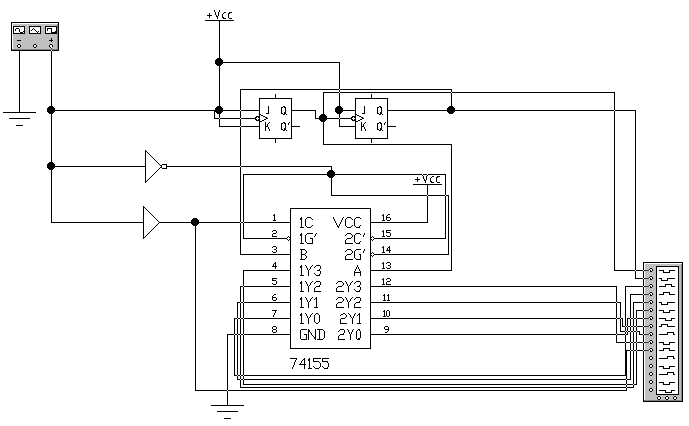

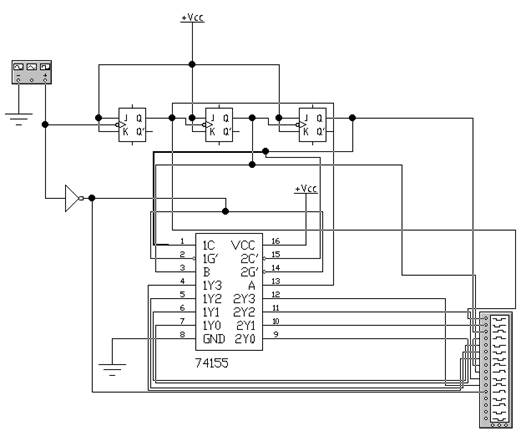

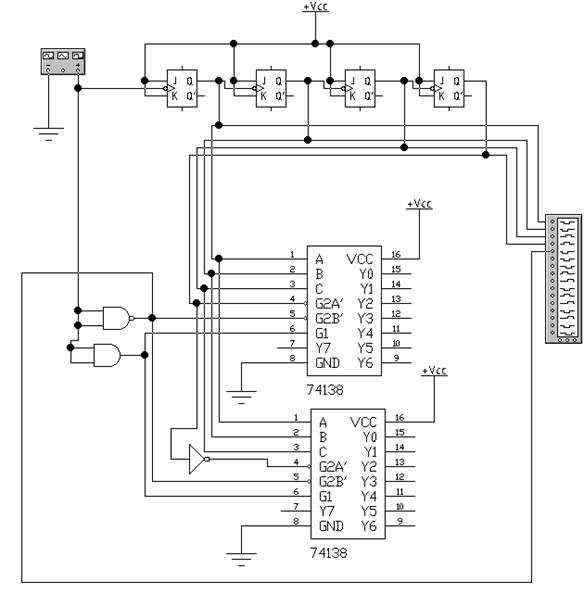

Задание №5. Собрать схему двухвходового дешифратора на базе микросхемы К555ИД4 (74155).

Таблица истинности.

|

A0 |

A1 |

1Y0 |

1Y1 |

1Y2 |

1Y3 |

2Y0 |

2Y1 |

2Y2 |

2Y3 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Задание №5.1. Собрать схему трехвходового дешифратора на основе микросхемы К555ИД4 (74155).

Таблица истинности.

|

A2 |

A1 |

A0 |

1Y0 |

1Y1 |

1Y2 |

1Y3 |

2Y0 |

2Y1 |

2Y2 |

2Y3 |

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

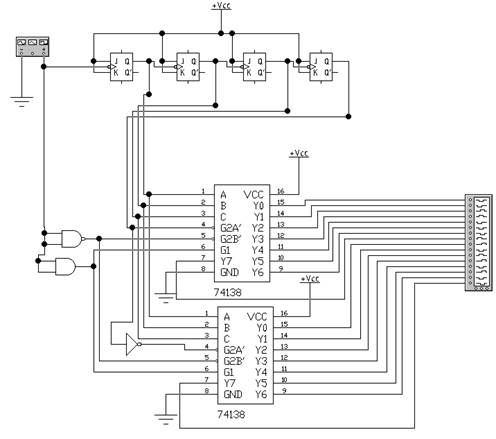

Задание №6. Исследовать работу дешифратора ИМС 533ИД7 (74138).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.