Введение ……………………………………………………………………………………..2

1. Описание работы схемы………………………………………………………….

2. Технические условия на проектирование ………………………4

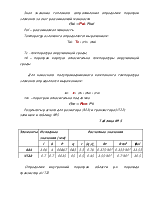

3. Расчет мощности, выделяемой на пленочных резисторах …….

4. Расчет геометрии пленочных резисторов …..………………..…6

5. Расчет сопротивлений контактных переходов …..……………11

6. Расчет плёночных емкостей………..…………………………...12

7. Расчет добротности конденсаторов….……

8. Выбор и обоснование навесных элементов ГИС

9 Разработка топологии ………………………………………….19

10 Расчет паразитных связей….………………………………...….16

11. Выбор и обоснование технологии изготовления схемы …….20

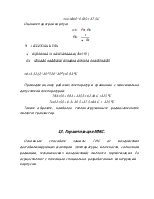

12. Тепловой расчет ИМС……………..…………………………...21

13. Герметизация ИМС……………………......…………………...23

13.1. Выбор способа проверки герметизации………...………..…23

Заключение ……….………………………………………….……. 24

Список используемой литературы ……..………………………....25

Целью курсового проекта является разработка конструкции интегральной микросхемы (ИМС) и технологического маршрута ее производства в соответствии с заданной в техническом задании схемой электрической принципиальной.

Последние годы развития микроэлектроники связанны с широким внедрением в производство больших и сверхбольших интегральных микросхем (БИС, СБИС), что обуславливает необходимость разработки новых технологических процессов и новых подходов при конструировании.

Технология интегральных микросхем представляет собой совокупность механических, физических, химических способов обработки различных материалов (полупроводников, диэлектриков, металлов), в итоге которой создается интегральная микросхема.

Интегральная микросхема – это конструктивно законченное изделие электронной техники, выполняющее определенную функцию преобразования информации и содержащее совокупность электрически связанных между собой электрорадиоэлементов (ЭРЭ), изготовленных в едином технологическом цикле.

По способу изготовления различают полупроводниковые и пленочные ИМС. В полупроводниковых ИМС все ЭРЭ и часть межсоединений сформированы в приповерхностном слое полупроводниковой подложки. В пленочных ИМС пассивные ЭРЭ изготовлены в виде совокупности тонких (менее 1 мкм) или толстых (10- 50 мкм) пленок, нанесенных на диэлектрическую подложку. Гибридные ИМС (ГИС) представляют собой комбинацию пленочных пассивных ЭРЭ с миниатюрными бескорпусными дискретными активными приборами (полупроводниковыми ИМС, транзисторами, диодами), расположенных на общей диэлектрической подложке.

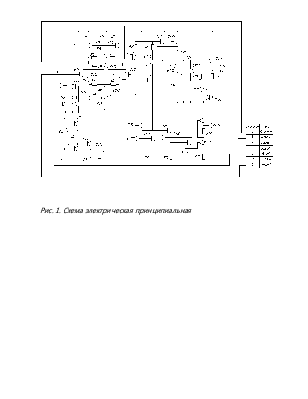

1. Описание схемы

Быстродействующий ОУ типа 140УД10 имеет скорость наростания входного напряжения 50 В\мкс и частоту единичного усиления 15МГц

Этот ОУ построен по трехкаскадной схеме . Для увеличения входного сопротивления первый диф. Каскад построен по схеме Дармингтона (транзисторы VT8,VT10,VT20,VT19). Для расширения полосы усиления в эмиттеры его усилительных транзисторов включены резисторы R7,R13. Входной каскад питается от ГСТ (VT13). Ток от транзистора VT13 поступает на специальную схему распределения, выполненную на транзисторе VT17, двухэмиттерном транзисторе VT12 и резисторах R8-R10. Транзистор VT12 работает в инверсном включении и обеспечивает током «подпитки» эмиттеры входных транзисторов.

Данная схема распределения обеспечивает малое изменение токов входного каскада во всем температурном диапазоне. Схема защиты входного каскада от высокого синфазного напряжения выполнена на транзисторах VT16,VT14, а транзисторы VT1,VT2,VT4, VT5 защищают входной каскад от перегрузки по дифферициальному сигналу. Транзисторы VT11,VT18 выполняют роль активной нагрузки входного каскада. Транзистор VT15 ограничивает уровень напряжения коллектор-база этих транзисторов.

Второй каскад также построен по дифферициальной схеме (транзисторы VT210,VT24). Активными нагрузками второго каскада служат транзисторы VT22,VT25. Режим по постоянному току каскада задается смещением транзисторов VT21,VT24 стабилизированным коллекторным напряжением входного каскада. Третий каскад усиления построен на транзисторах VT34,VT30,VT31, VT27, нагрузкой которых служит ГСТ на транзисторе VT29, ток которого стабилизирован падением напряжения на диоде, образованном соединением второго коллектора транзистора с его базой. Выходной каскад построен на двухэмиттерном транзисторе VT38 и транзисторе VT39. Второй эмиттер транзистора VT38 служит для управления выходным транзистором.

Такая схема увеличивает быстродействие выходного транзистора. Транзисторы VT32,VT33,VT38 осуществляют защиту выходного каскада ОУ от перегрузки в режиме короткого замыкания выхода. Транзистор VT33 обеспечивает защиту схемы ОУ от триггерного режима и в момент перегрузки шунтирует транзистор VT39.

Для улучшения передачи высоких частот в схеме ОУ имеются три конденсатора. Конденсатор С1,шунтируя на высокой частоте одну половину входного дифференциального каскада, тем самым превращает его дифференциальный выход в одиночный. Далее высокочастотный сигнал через конденсатор С2 обходит второй дифференциальный каскад, построенный на низкоскоростных транзисторах.

Высокочастотная составляющая сигнала с выхода первого каскада поступает сразу на базу транзистора третьего каскада

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.