Министерство общего и профессионального образования РФ

Хабаровский Государственный Технический Университет

Кафедра ВМ

Расчетно-графическая работа № 2

по курсу: Теория проектирования ЭВМ и систем

Вариант 2

Выполнил: студент гр. ВМ-51

Лазебник В.Н.

Проверил: преподаватель

Березин В.В.

1998 г.

Задание: спроектировать мультипроцессорный арбитр шины (шина со многими активными процессорами). Имеются 5 входов (RA0…RA4) запроса шины для процессоров типа А и 5 выходов представления шины (BG0…BG4). Чем выше номер входа запроса, тем ниже приоритет этого запроса (т.е. наивысший приоритет у запроса RA0).

Кроме этого имеется 3 входа запроса (RB0…RB2) шины с процессорами типа В с выходами представления шины (BG5..BG7) с аналогичными правилами приоритетов, однако шина предоставляется процессорам типа В только тогда, когда нет запросов от процессоров типа А.

Предусмотреть входы сброса и тактирования арбитра, тип ПЛИС – по выбору.

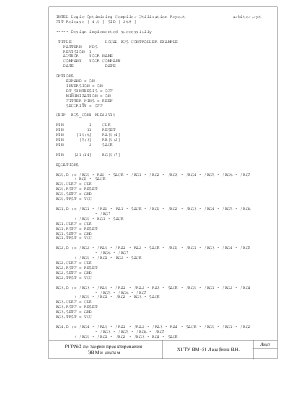

INTEL Logic Optimizing Compiler Utilization Report arbiter.rpt

FIT Release [ 4.0 ] SID [ 268 ]

***** Design implemented successfully

TITLE LOCAL BUS CONTROLLER EXAMPLE

PATTERN PDS

REVISION 1

AUTHOR YOUR NAME

COMPANY YOUR COMPANY

DATE DATE

OPTIONS

EXPAND = ON

INVERSION = ON

DT_SYNTHESIS = OFF

MINIMIZATION = ON

FITTER_PINS = KEEP

SECURITY = OFF

CHIP BUS_CON1 PLD22V10

PIN 1 CLK

PIN 11 RESET

PIN [10:6] RA[0:4]

PIN [5:3] RB[0:2]

PIN 2 SACK

PIN [21:14] BG[0:7]

EQUATIONS

BG0.D := /BG0 * RA0 * SACK * /BG1 * /BG2 * /BG3 * /BG4 * /BG5 * /BG6 * /BG7

+ BG0 * SACK

BG0.CLKF = CLK

BG0.RSTF = RESET

BG0.SETF = GND

BG0.TRST = VCC

BG1.D := /BG1 * /RA0 * RA1 * SACK * /BG0 * /BG2 * /BG3 * /BG4 * /BG5 * /BG6

* /BG7

+ /BG0 * BG1 * SACK

BG1.CLKF = CLK

BG1.RSTF = RESET

BG1.SETF = GND

BG1.TRST = VCC

BG2.D := /BG2 * /RA0 * /RA1 * RA2 * SACK * /BG0 * /BG1 * /BG3 * /BG4 * /BG5

* /BG6 * /BG7

+ /BG0 * /BG1 * BG2 * SACK

BG2.CLKF = CLK

BG2.RSTF = RESET

BG2.SETF = GND

BG2.TRST = VCC

BG3.D := /BG3 * /RA0 * /RA1 * /RA2 * RA3 * SACK * /BG0 * /BG1 * /BG2 * /BG4

* /BG5 * /BG6 * /BG7

+ /BG0 * /BG1 * /BG2 * BG3 * SACK

BG3.CLKF = CLK

BG3.RSTF = RESET

BG3.SETF = GND

BG3.TRST = VCC

BG4.D := /BG4 * /RA0 * /RA1 * /RA2 * /RA3 * RA4 * SACK * /BG0 * /BG1 * /BG2

* /BG3 * /BG5 * /BG6 * /BG7

+ /BG0 * /BG1 * /BG2 * /BG3 * BG4 * SACK

BG4.CLKF = CLK

BG4.RSTF = RESET

BG4.SETF = GND

BG4.TRST = VCC

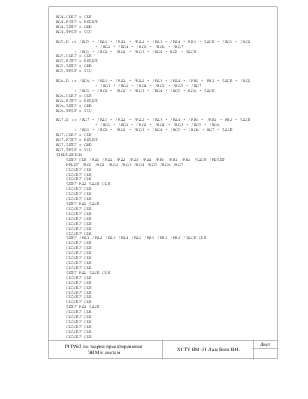

BG5.D := /BG5 * /RA0 * /RA1 * /RA2 * /RA3 * /RA4 * RB0 * SACK * /BG0 * /BG1

* /BG2 * /BG4 * /BG3 * /BG6 * /BG7

+ /BG0 * /BG1 * /BG2 * /BG3 * /BG4 * BG5 * SACK

BG5.CLKF = CLK

BG5.RSTF = RESET

BG5.SETF = GND

BG5.TRST = VCC

BG6.D := /BG6 * /RA0 * /RA1 * /RA2 * /RA3 * /RA4 * /RB0 * RB1 * SACK * /BG0

* /BG1 * /BG2 * /BG4 * /BG3 * /BG5 * /BG7

+ /BG0 * /BG1 * /BG2 * /BG3 * /BG4 * /BG5 * BG6 * SACK

BG6.CLKF = CLK

BG6.RSTF = RESET

BG6.SETF = GND

BG6.TRST = VCC

BG7.D := /BG7 * /RA0 * /RA1 * /RA2 * /RA3 * /RA4 * /RB0 * /RB1 * RB2 * SACK

* /BG0 * /BG1 * /BG2 * /BG4 * /BG3 * /BG5 * /BG6

+ /BG0 * /BG1 * /BG2 * /BG3 * /BG4 * /BG5 * /BG6 * BG7 * SACK

BG7.CLKF = CLK

BG7.RSTF = RESET

BG7.SETF = GND

BG7.TRST = VCC

SIMULATION

SETF CLK /RA0 /RA1 /RA2 /RA3 /RA4 /RB0 /RB1 /RB2 /SACK /RESET

PRLDF /BG0 /BG1 /BG2 /BG3 /BG4 /BG5 /BG6 /BG7

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RA2 SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RA0 SACK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF /RA1 /RA2 /RA3 /RA4 /RA0 /RB0 /RB1 /RB2 /SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RA0 SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RA1 SACK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RB0 SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RB2 SACK CLK

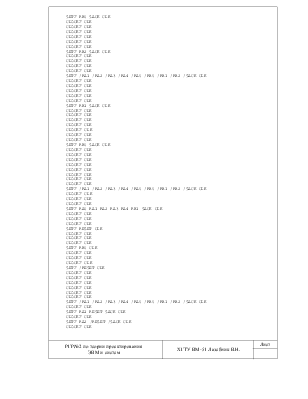

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF /RA1 /RA2 /RA3 /RA4 /RA0 /RB0 /RB1 /RB2 /SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RB1 SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RB0 SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF /RA1 /RA2 /RA3 /RA4 /RA0 /RB0 /RB1 /RB2 /SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RA0 RA1 RA2 RA3 RA4 RB1 SACK CLK

CLOCKF CLK

CLOCKF CLK

CLOCKF CLK

SETF RESET CLK

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.