Режим прерывания программы.

У каждого устройства есть:

Регистр состояния

Регистр данных

В регистре состояния для организации доступа к памяти достаточно иметь 1 разряд (бит готовности), который в режиме приема, при включении питания бит готовности сбрасывается на 0; в режиме передачи, при включении бит готовности выставляется в 1, после передачи – в 0.

Для повышения производительности используется буфер данных, в этом случае передача происходит блоками.

Для работы в режиме реального времени используется передача по прерыванию.

Основы: ЦП нет необходимости отслеживать регистр состояния. В регистр состояния добавляется 1 бит разрешения прерывания (по сигналу ЦП RES в регистре состояния этот бит выставляется в 0, т.е. прерывания запрещены. На этапе загрузки выставляются в 1 необходимые регистры состояния). Т.е. ЦП имеет состояния разрешения или запрещения обработки прерывания.

Одноуровневая система обработки прерывания, один вход требования прерывания . Если ЦП зашел в программу обработки прерывания, то его невозможно вернуть, поэтому для организации вложенных прерываний используются дополнительные команды. Иначе применяется последовательная обработка прерывания.

Многоуровневая система обработки прерывания. ЦП может находиться на одном из 8 уровней приоритета. В любой момент времени, может обрабатываться прерывание , в зависимости от приоритетности. Если приоритет больше, то используется вложенное прерывание.

0-3 – уровни приоритета прерываний программ;

4-7 – уровни приоритета прерываний внешних устройств.

Т.е. если уровень приоритета ЦП равен 7, то его никто не может прервать.

Если во время обработки прерывания на процессор поступило другое прерывание с большим приоритетом, то процессор предоставляет ресурсы прерыванию после обработки текущей команды.

Для одних ВМ(с малым быстродействием) используется стек: в него при обработке прерывания загружаются текущие указатель команды и словосостояние , а на магистраль данных загружаются новые.

Для других(более новых) происходит автоматическое переключение на использование второго указателя команд и словосостояние.

В случае поступления сигналов от двух устройств одонго уровня приоритета,для корректной работы используется загрузка в словосостояние ЦП содержимого уровня приоритета.

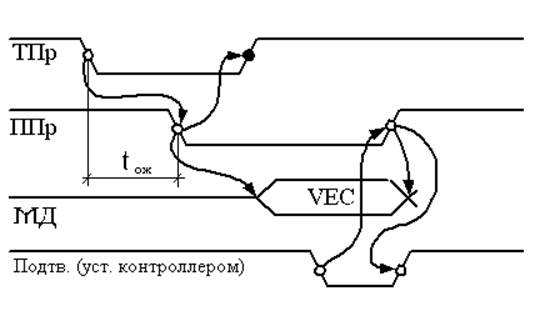

Временная диаграмма.

Когда устройство готово к обмену, и если ему разрешены прерывания, то формируется требование прерывания (ТПр), а по нему – подтверждение прерывания (ППр)( Сигнал ППр появляется если устройство имеет приоритет выше чем у процессор.

Если приоретет не позволяет то tож может быть до бесконечности, а если позволяет то tож равно времяни выполнения команды). Получив сигнал ППр, контроллер снимает сигнал ТПр, значение счетчика команд записывается в стек, по номеру вектора прерывания загружается новое значение счетчика команд и слово состояния

Плюсы: проще устройство контроллеров;

Мину: проигрыш в быстродействии

Прямой доступ.

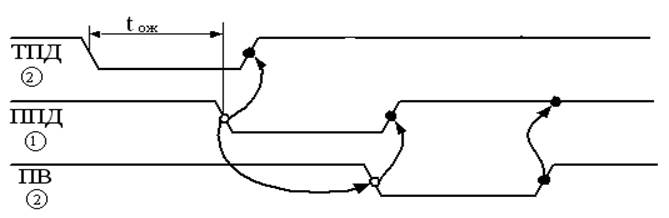

При таком обмене формируется сигнал требования прямого доступа (ТПД), который поступает непосредственно на процессор, который, в свою очередь, формирует сигнал подтверждения прямого доступа (ППД). tож – время ожидания – завершение текущего цикла процессора (максимальное время ожидания – цикл процессора). Сигнал ППД может формироваться по различным схемам и формирует сигнал подтверждение выбора (ПВ). Получив сигнал подтверждения выбора, процессор отключается от магистрали на время, пока сигнал активен. Это самый быстрый способ обмена при передаче больших массивов данных.

Временная диаграмма.

Однокристальные контролеры.

Этапы развития:

I. На кристалле порядка 20 выводов портов ввода/вывода, которые могут быть программируемы. В ядре кристалла содержится минимум один таймер – функция спящая собака(счетчик по времени). В некоторых системах встраиваются ЦАП и АЦП.

II. Увеличение производительности. Как правило это все RISC системы. Основной недостаток: последовательное выполнение команд(специализированные команды).

ДСП от MOTOROLA

При любых обрабатываемых сигналах используется их суммирование. В наличии имеются две магистрали данных. Поэтому операнды А и В проводятся параллельно. Используется для ЦП 900 МГц.

III. Появление SRAM технологии – программирование любых функций – свободный кристалл . При развитии технологии – логическая ячейка памяти.

PDL – ограниченное быстродействие, т.к. однокристальное программирование.

FPGA – SRAM технология, зависящая от вкл/выкл питания, при включении питания чип программируется с малой микросхемы, восстанавливает свои функции.

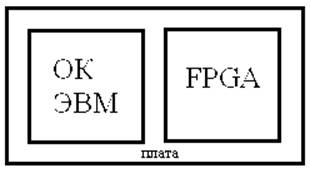

Новинка:

Технология на кристале.

OK ЭВМ – программирование,

FPGA – выполнение элементарных функций.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.