«DEC Архитектур: Методы адресации»

1. Архитектурный особенности DEC

Семейство процессоров DEC базируются на принципах CISC архитектуры, имеют обычно 16-разрядную шину адреса, восемь 16-разрядных регистров общего назначения R0 – R7. Причём R7 - счетчик команд PC, R6 - указатель стека SP. Как упоминалось ранее, за счет того, что регистры PC и SP относятся к набору регистров общего назначения, появилась возможность проводить с ними любые операции, как с обыкновенными данными.

Как правило, дешифратор инструкций в DEC процессорах, имеет перепрограммируемую матрицу состояний (реализовано на ПЛМ), которая даёт возможность программисту реализовать в процессоре свой собственный набор команд, оптимизированный для конкретных задач.

2. Адресное пространство DEC

![]()

Адреса векторов прерывания

![]()

Область программ

![]()

Страница Ввода-Вывода

Note: Если адресация чётная (наличие 0 в старшем разряде кода команды) работаем с двойным байтом (16 бит), если нечётная (1 в старшем разряде кода) работаем с байтом данных. См. примеры на основе работы команды MOV ниже.

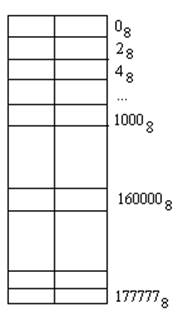

Все адреса представлены в восьмиричной системе. Максимальное адресное пространство для рассматриваемой системы состовляет 08 -1777778 или 016 - FFFF16, т.е. 65536 байт пространства.

Первые адреса системы [000000:0009998] – адреса векторов прерыва-ния, которые являются строго определёнными и не подлежат изменению.

[0010008:1599998] – область для хранения программ.

[1600008:1777778] – страниза адресов устройств ввода-вывода.

3. Формат представления команд

3.1. Безадресный

15 0

|

Команда |

3.2. Одноадресная команда

15 0

|

Команда |

адрес |

15 0

|

JMP |

ADDRESS |

3.3. Двухадресный

15 0

|

Команда |

Адрес источника |

Адрес приёмника |

4. Формат представления адреса и методы адресации

Поле адреса условно разбивается на два подполя:

|

Метод адресации |

Номер РОНа |

У микропроцессоров DEC существует четыре основные метода адресации, каждый из которых может использоваться как в режиме прямой, так и в режиме косвенной адресации (и того всего 8-мь):

§ Регистровая прямая адресация (0 x);

§ Регистровая косвенная адресация (1 x);

§ Автоикрементная прямая (2 x);

§ Автоикрементная косвенная (3 x);

§ Автодекриментная прямая (4 x);

§ Автодекрементная косвенная (5 x);

§ Индексная прямая (6 x);

§ Индексная косвенная (7 x);

Прямой регистровый метод адресации (МА): на примере команды пересылки MOV R0, R1, выполняющейся за 1 машинный цикл.

|

01 |

00 |

01 |

|

Код команды |

Нуль в первом разряде показывает, что МА источника – прямой, во втором, на то, что источником является R0 |

Нуль в первом разряде показывает, что МА приемника – прямой, единица во втором – показывает номер регистра (т.е. R1) |

Косвенный регистровый МА:

На примере команды MOV R0,(R1), два машинных цикла. В ходе выполнение данной команды произойдет перемещения содержимого регистра R0 в устройтво, косвенно адресуемое регистром R1, т.е. по адресу хранящемуся в регистре R1.

Источник Приёмник

|

01 |

00 |

11 |

Первая число в полях “источник” и “приёмник” характеризует тип адресации – прямой (0) или косвенный (1).

Прямой автоинкрементный МА (прединкрементный):

На примере команды MOV +(R3),R2. Вначале содержимое R3 увеличивается на 2 (т.к. чётная адресация – 0 1), затем происходит выставление нового содержимого R3 на адресную шину, запрашиваемое косвенно число затем записывается в R2. Содержимое PC после выполнения команды также увеличивается на 2.

Порядок выполнения: R3:=R3+2; PC:=PC+2; R2:=(R3).

Источник Приёмник

|

01 |

23 |

02 |

Косвенный автоинкрементный МА (прединкрементный):

На примере команды пересылки MOV +((R3)),R2. Вначале происходит увеличение содержимого R3 на 2. В регистр R2 записывается число, находящееся по адресу, который хранится в ячейки памяти, косвенно адресуемой R3. Таким образом: R3:=R3+2; R2:=((R3)); PC:=PC+2.

Источник Приёмник

|

01 |

33 |

02 |

Автодекрементный метод адресации:

Полностью аналогичен автоинкрементному, но вместо увеличения на два, происходит уменьшение на два (при использовании чётной адреса-ции). Для прямого: MOV –(R3),R2 Для косвенного: MOV –((R3)),R2.

Индексный прямой МА:

На примере команды MOV A(R3),R2. Суть индексного прямого метода адресации заключается в том, что содержимое регистра R3 смещенается на значение A, затем полученное значение является адресом блока данных. Эти данные косвенно адресуемые R3+A записываются в регистр R2.

Источник Приёмник

|

01 |

63 |

02 |

Таким образом получаем: R2 <- (R3+A)

Индексный косвенный МА:

Аналогично индексному прямому МА, только R2 <- ((R3+A))

Источник Приёмник

|

01 |

73 |

02 |

Список дополнительной литературы:

1. Лин Вэн PDP-11 и VAX-11 Архитектура ЭВМ и программиррование на языке ассемблера: производственное издание. - М.: Радио и связь, 1989. - 317с.

2. Каган Б.М., Сташин В.В. Основы проектирования микропроцессорных устройств автоматики.-М.: Энергоатомиздат, 1987.-304с.:ил.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.