Если процессор находился в состоянии THUMB, когда произошло исключение, он переключается в состояние ARM, в тот момент когда PC загружает адрес вектора исключения.

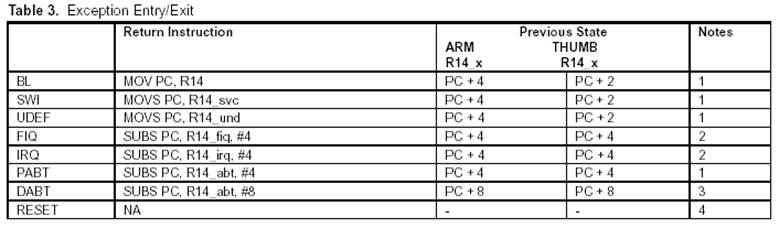

Таблица 3. Основные исключения.

Порядок возврата из исключения.

1. Перемещает значение регистра Link Register , минус соответствующее смещение, в PC. (Смещение зависит от типа исключения).

2. Возврат значения SPSR в CPSR.

3. Разрешаются исключения, если они были запрещены установкой соответствующих флагов.

Явное переключение в состояние THUMB не требуется, т.к. при восстановление CPSR бит Т устанавливается в то значение, которое было до исключения.

Примечания

1. PC соответствует адресу вызова инструкции BL/SWI/Undefined, при аварийном прекращение работы.

2. PC соответствует адресу вызова команды, которая не выполнилась, по причине возникновения FIQ или прерываний.

3. PC соответствует адресу команды Load или Store, при аварийном прекращении работы с данными.

4. Значение регистра R14_svc после сброса неизвестно.

FIQ

FIQ (Быстрые прерывания) исключение, предназначенное для поддержания передачи данных, или выполнения потока команд, В состоянии ARM имеет зарезервированные регистры, для минимизации потерь при переключении.

FIQ управляются сигналом nFIQ. Переключение может быт синхронным или асинхронным, в зависимости от состояния сигнала ISYNC. Когда ISYNC имеет низкий уровень, nFIQ и nIRQ асинхронны.

Независимо от того, произошло ли исключение в ARM или Thumb состояния, обработчик FIQ должен запретить другие прерывание, выполняя команду

SUBS PC, R14_fiq, #4

FIQ могут быть заблокирован, установлением флага F CPSR’s (В пользовательском режиме это запрещено). Если флаг F известен, ARM7TDMI проверяет низкий ли уровень на выводе FIQ синхронно в конце каждой команды.

Прерывания.

Прерывание – исключение, низким уровнем на вводе nIRQ. Прерывания имеет более низкий приоритет, чем FIQ и замаскированы при выполнении FIQ. Они могут быть заблокировано в любое время, установлением бита I в CPSR, (В пользовательском режиме невозможно устанавливать биты).

Независимо от того, было ли исключение введено от ARM или состояния Thumb, обработчик прерываний, возвращаясь из прерывания, выполняет команду

SUBS PC, Р14_fiq, #4

Аварийное прекращение работы

Аварийное прекращение работы указывает, что текущее обращение к памяти не может быть завершено. Это может быть объявлено внешним сигналом Abort. ARM7TDMI отслеживает аварийные ситуации в течение циклов обращения памяти.

Существует два типа аварийного прекращения работы:

Аварийное прекращение работы происходит в течение выбора команды.

Аварийное прекращение работы с данными происходит в течение доступа к данным.

Если аварийное прекращение работы происходит при выборе команды, команда назначается как недопустимая, но исключение не произойдет, пока команда не достигнет вершины конвейера.

Если аварийное прекращение работы происходит при чтении данных, предпринятое действие зависит от команды:

1. При одной передачи данных команды (LDR, STR) записывают назад изменения в регистры, и сообщает обработчику о прекращение работы.

2. Инструкция (SWP) прерывается, как если бы она не выполнялась.

3. Блочные команды передачи данных (LDM, STM) заканчиваются. Если с отложенной записью установлен, основа модифицирована. Если команда произошла при перезаписи данных, то перезапись отменяется. Вся перезапись регистров предотвращается после того, как произошло аварийное прекращение работы, это отмечается в регистре R15, сохраняющий инструкцию LDM при прерывание работы.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.