Основы

2.1 Аппаратная модель

Очень смешно проектировать учебный компьютера без подсчета стоимости аппаратного обеспечения и длины критичных путей. Это подобно тому, что мы идем за покупками, не глядя на ценники. В этой книге мы определим и проанализируем аппаратное обеспечение для модели из [MP95]. Это модель на уровне вентилей, которая дает, по крайней мере, грубую оценку.

2.1.1 Составляющие

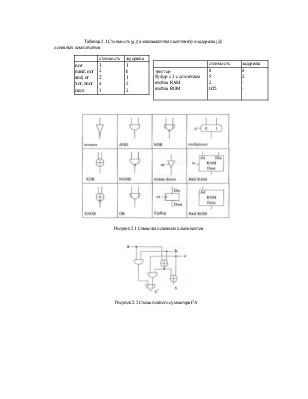

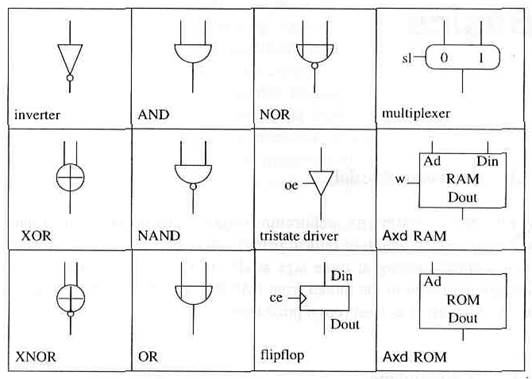

В модели пять типов основных компонентов, а именно: вентили, триггеры (flipflops), буферы с тремя состояниями (tristate drivers), RAM и ROM. Стоимости и задержки основных компонентов перечислены в таблице 2.1. Они нормализованы относительно стоимости и задержки 1-битного инвертора. Для основных компонентов мы используем символы на рисунке 2.1.

Сигналы разрешения синхронизации ce (clockenable) триггеров и регистров, сигналы разрешения вывода oe (outputenable) буферов с тремя состояниями и сигналы записи w (write) RAM – всегда активны (высокие). RAM имеют раздельные порты входа и выхода данных. Принимается, что все триггеры синхронизируются в каждом цикле; таким образом, они не нуждаются в изображении входов синхронизации.

RAM с Aадресами и d-битными данными имеет стоимость

![]()

Таблица 2.1 Стоимость [g] (в эквивалентных вентилях) и задержка [d] основных компонентов

|

стоимость |

задержка |

|

|

not |

1 |

1 |

|

nand, nor |

2 |

I |

|

and, or |

2 |

1 |

|

xor, xnor |

4 |

2 |

|

mux |

3 |

2 |

|

стоимость |

задержка |

|

|

триггер |

8 |

4 |

|

буфер с 3-состоянием |

5 |

2 |

|

ячейка RAM |

2 |

- |

|

ячейка ROM |

0.25 |

- |

Рисунок 2.1 Символы основных компонентов

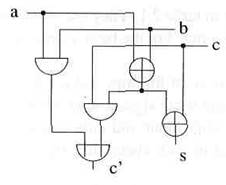

Рисунок 2.2 Схема полного сумматора FA

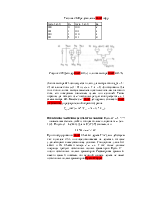

Таблица 2.2 Времена чтения и записи регистров и RAM; dramозначает время доступа RAM.

|

|

|

|

|

и задержку |

Для конструкций файлов регистров, мы используем 3-портовые RAM, способные выполнять два чтения и одну запись за один цикл. Если в одном цикле производится чтение и запись по одному и тому же адресу, тогда выходные данные операции чтения остаются неопределенными.

Стоимость и задержка этих многопортовых RAM

|

|

![]()

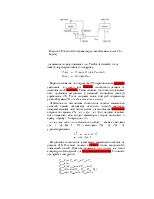

Схема на рисунке 2.2 имеет стоимость Сfaи задержку dfa,

|

|

2.1.2 Времена циклов

При вычислении времен циклов, мы определяем для чтений и записей в регистры и RAM времена, определенные в таблице 2.2. Обратите внимание, что мы начинаем и заканчиваем подсчет циклов на данном этапе в то время, когда выводы регистров имеют новые значения. Константа δ ответственна за времена установки и удержания; мы используем δ = 1 .

|

Пример 2.2 |

Предположим, что схема Sимеет задержку dSи RAM Rимеет время доступа dram . Тогда четыре схемы на рисунке 2.3 имеют времена циклов

|

|

2.1.3 Иерархические конструкции

Определить конструкции иерархическим или даже рекурсивным способом - обычная практика. Также не вызывает проблем описать стоимость или задержку иерархических конструкций системами уравнений. Для рекурсивных конструкций получаем рекурсивные системы дифференциальных уравнений. Раздел 2.3 этой главы содержит многочисленные примеры.

Решение систем таких уравнений в закрытой форме – обычная работа при анализе алгоритмов, если системы малы. Конструкции процессоров содержат дюжины листов схем. Мы даже не будем пытаться решать связанные системы уравнений в закрытой форме. Вместо этого мы переведем простым путем уравнения в программы на С и позволим компьютеру сделать эту работу.

Выполнение компьютерной программы – специфическая форма эксперимента. Научные эксперименты должны быть воспроизводимы настолько легко, насколько это возможно. Поэтому все программы на С, связанные с конструкциями из этой книги, доступны на нашем web-сайте1. Читатель может легко проверить анализ конструкций, анализ модифицированных конструкций, или заново оценить конструкции с новым набором задержек и стоимостей компонентов.

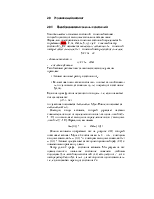

2.1.4 Нотации для формул задержек

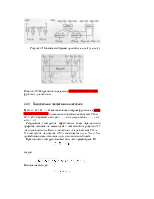

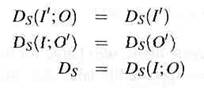

Пусть S– схема со входами I и выходами Oкак показано на рисунке 2.4. Часто желательно анализировать задержку DS(I';О') от некоторого подмножества I' входов к некоторому подмножеству O' выходов. Это – максимальная задержка пути pот входа I' к выходу O'. Мы используем сокращения

|

|

|

1 http://www-wjp.cs.uni-sb.de/infо/papers/#books |

Схемы Sне существуют по отдельности; их входы и выходы соединены с регистрами или RAM, возможно через длинные пути. Мы обозначим через AS(I'; О') максимальную задержку пути, который начинается в регистре или RAM, входит в Sчерез I' и покидает Sчерез O’. Мы называем AS(I';О') – накопленная задержка(accumulateddelay). Если все входы I' напрямую соединены с регистрами, мы имеем

|

|

Рисунок 2.3 Четыре типа передачи между регистрами и RAM

|

|

Рисунок 2.4 Пути через схему S. I' – подмножество ее входов I, и O' – подмножество ее выходов O.

|

Пример 2.3 |

Аналогично, обозначим через TS(I' ; O') максимальное время цикла, требуемое для циклов (циклами) через I' и O'. Если I' = I или O' = О сокращаем, как показано выше.

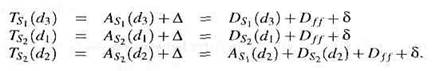

Схема Sc на рисунке 2.5 включает три цикла:

• выход из схемы S1через выход d3 ,

• вход в схему S2 через вход d1 ,

• вход в схему S2 через вход d2 . Таким образом, время цикла Scможет быть выражено как

TSc = mах{TS1(d3) , TS2(d1) , TS2(d2)},

|

|

|

Рисунок 2.5 Схемотехника Sc |

с

2.2 Представления чисел и основные схемы

2.2.1 Натуральные числа

Для битов x € {0,1} и натуральных чисел n, мы обозначим через xn строку, состоящую из n копий x. Например, 03 = 000 and 15 = 11111. Обычно, мы нумеруем (индексируем) биты строки а € {0,1}n справа

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.