1. Исследование регистров.

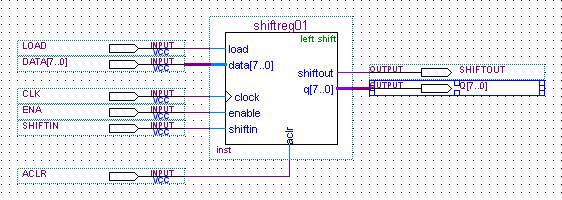

Рис. 1. Схема регистра.

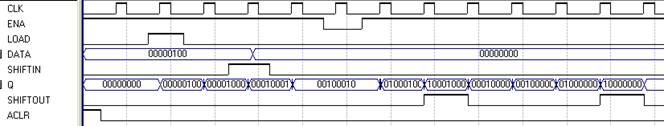

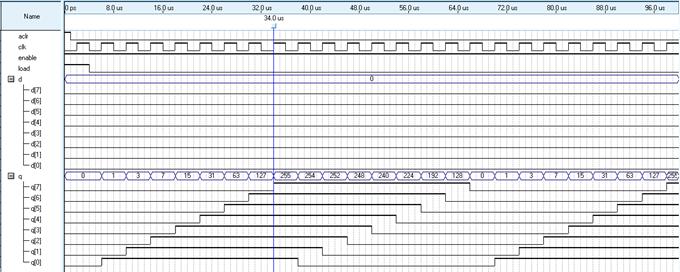

Рис. 2. Диаграмма работы регистра.

ENA = 0 – режим хранения (на 6 такте);

ENA =1, LOAD =1 – режим параллельной загрузки(на 2 такте);

На входе SHIFTOUT старший разряд Q[].

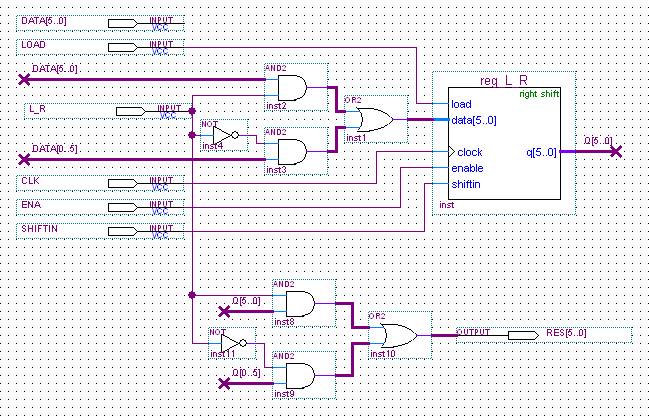

Рис. 3. Схема регистра.

Вход L_R управляет направлением сдвига: L_R=0 сдвиг происходит влево, L_R=1 сдвиг происходит вправо.

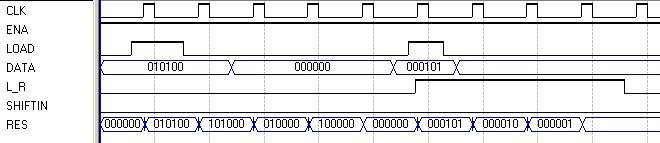

Рис. 4. Диаграмма работы регистра сдвигающего вправо и влево.

1 такт – параллельная загрузка «010100»;

2-5 такт – сдвиг влево;

6 такт – параллельная загрузка «000101»

7-8 такт – сдвиг вправо.

1.3)Исследование счетчика Джонсона на базе мегафункции LPM_SHIFTREG.

Ставим инвертор в обратную связь схемы.

Рис 2.3.1 Счетчик Джонсона в Quartus II

Рис 2.3.2 Моделирование работы счетчика Джонсона в Quartus II

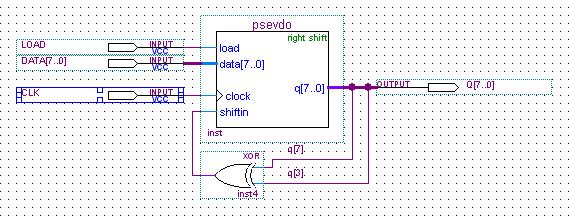

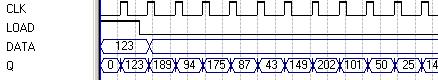

Рис. 7. Схема генератора псевдослучайных чисел.

Рис. 8. Диаграмма генератора.

2. Исследование сумматоров.

2.1) Сумматор-вычитатель на основе мегафункций LPM_ADD_SUB.

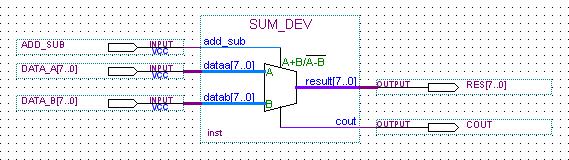

Рис. 9. Схема сумматора-вычитателя.

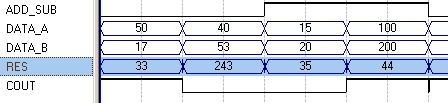

Рис. 10.Диаграмма работы сумматора-вычитателя.

Работа на вычитание:

50-17=33, COUT=1 – заема не было;

40-53=-13(243 – в доп. коде), COUT=0 – заем был;

Работа на сложение:

15+20=35, COUT=0 – заема не было;

100+200=256+44, COUT=1 – был перенос;

2.2) Двоично-десятичный сумматор.

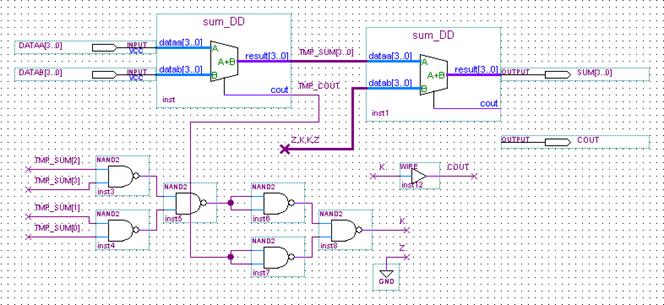

Рис. 11. Двоично-десятичный сумматор на двух четырёхразрядных двоичных сумматорах.

Рис. 12.Диаграмма работы двоично-десятичного сумматора.

3 + 5 = 8

6 + 8 = 10 + 4, COUT=1;

Сумматор функционирует правильно.

2.3) Двухтетрадный двоично-десятичный накапливающий сумматор.

Рис. 13. Двухтетрадный двоично-десятичный накапливающий сумматор.

SUM_1[] – младшая тетрада, SUM_2[] – старшая тетрада

Рис. 14. Диаграмма работы двухтетрадного двоично-десятичного накапливающего сумматора.

1 такт: 0(0000,0000) + 20(0010,0000)

2 такт: 20(0010,0000) + 21(0010,0001) = 41(0100,0001)

3 такт: 41(0100,0001) + 54(0101,0001) = 95 (1001,0101)

Сумматор функционирует правильно.

3. Вывод:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.