Рис.2.

1.3. Выполните полную компиляцию устройства. Проанализируйте предупреждения компилятора.

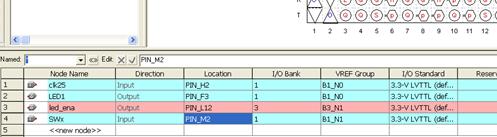

Таблица 1. Таблица подключения переключателей стенда к выводам СБИС ПЛ EP2C8F256C8.

|

Имя переключателя |

sw8 |

sw7 |

sw6 |

sw5 |

sw4 |

sw3 |

sw2 |

sw1 |

|

Имя вывода |

M2 |

N7 |

M1 |

N6 |

M3 |

K7 |

L3 |

N4 |

2. Создание файла логического анализатора.

Откройте окно настройки логического анализатора SignalTap II (Tools / SignalTap II Logic Analyzer). Выполните настройку логического анализатора для исследования процесса дребезга:

2.1. в окне задания наблюдаемых сигналов вызовите Node Finder и, установив маску Pins: all, выберите для наблюдения входной вывод SWx. Щелкнув правой кнопкой в столбце Trigger Conditions, установите условия захвата Basic по фронту или спаду сигнала SWx.

2.2. В окне задания параметров (Signal Configuration) сигнал Clock ― частота выборки ― сигнал Synchr проекта; объем выборки (Sample Depth) -1К. Остальные установки оставьте без изменения.

2.3. Выполните полную компиляцию проекта.

2.4. Откройте окно логического анализатора. В окне настройки JTAG выберите используемое средство загрузки, загружаемый файл и запустите программирование. После окончания программирования убедитесь, что сигнал с переключателя передается на светодиод.

2.5. Задайте режим непрерывной работы логического анализатора и, переключая переключатель, наблюдайте записываемые логическим анализатором сигналы. Для пяти переключений в состояние 1 пяти переключений в состояние 0 определите длительность процесса переключения и количество импульсов дребезга. Результаты занесите в таблицу.

2.6. Для двух выбранных файлов наблюдаемых логическим анализатором данных выполните экспорт в формат .vwf. Выполните File / Export. В открывшемся окне задайте имя файла, формат .vwf, период Т = 1..10us в соответствии с заданием.

2.7. С помощью редактора временных диаграмм выполните сравнение полученных файлов (View / Compare to Waveforms in File).

2.8. Проанализируйте полученные результаты.

3. Анализ минимальной длительности импульсов дребезга.

Для анализа минимальной длительности импульсов дребезга следует задать максимальную разрешающую способность логического анализатора, выбрав максимальную тактовую частоту записи в кольцевой буфер, и выполнить запись сигналов с выхода переключателя.

3.1. Определите максимальную тактовую частоту работы проекта по п.2. Она определит максимальную тактовую частоту записи в кольцевой буфер логического анализатора SignalTapII. Вместо счетчика-делителя в схеме рис.1 установите PLL, увеличивающий входную тактовую частоту 25 МГц до значения, близкого к максимальной тактовой частоте. При настройке с помощью MegaWizard мегафункции ALTPLL, расположенной в папке I/O библиотеки мегафункций QuartusII оставьте только входной порт inclock0, для которого задайте частоту 25 МГц, и выходной порт с0, установив для него требуемую выходную частоту. Символ настроенной мегафункции ALTPLL показан на рис.3.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.