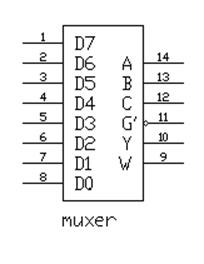

Нижче приводиться приклад

дослідження функціоальних властивостей і прикладів використання мікросхеми

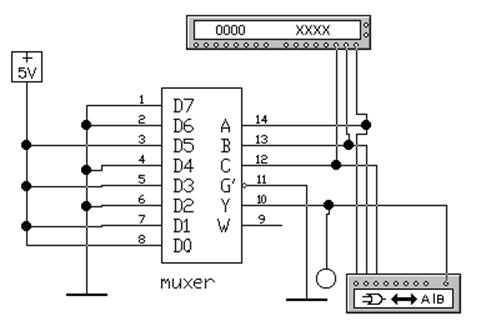

мультиплексора, що зображена на рисунку під назвою MUXERНижче приводиться

коротке описання його роботи

Нижче приводиться приклад

дослідження функціоальних властивостей і прикладів використання мікросхеми

мультиплексора, що зображена на рисунку під назвою MUXERНижче приводиться

коротке описання його роботи

Мультиплексор (селектор джаних) має дванадцять входів і два виходи. Входи включають в себе вісім ниток передачі даних, три керуючі входи, які краще назвати входами адресації, а також вхід дозволу роботи, який краще назвати керуючим входом. В залежності від значень двійкового коду, представленого на адресних входах, вибирається відповіднимй вхід, який передає свої значення на прямий вихід Y в прямому коді, а на вихід W – в інверсному. Керуючий сигнал G’ своїм низьким вхідним рівнем сигналу дозволяє мультиплексору виконувати заложену в ньому функцію, а високим- навпаки, забороняє його роботу.

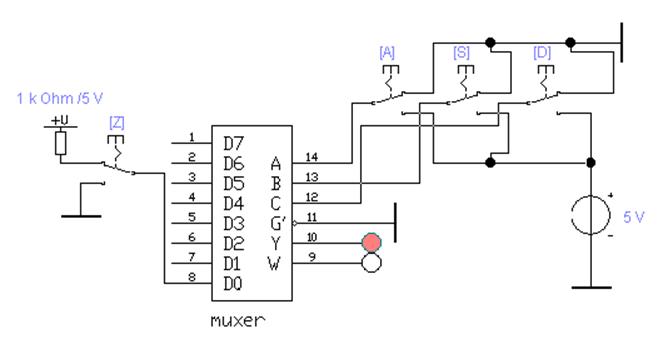

Приципова схема, для проведення досліджень повинна демонстувати роботу мультиплексора при всіх можливих станах, які забезпечуються інверсним входом дозволу роботи G а також адресними входами А, В, С.

|

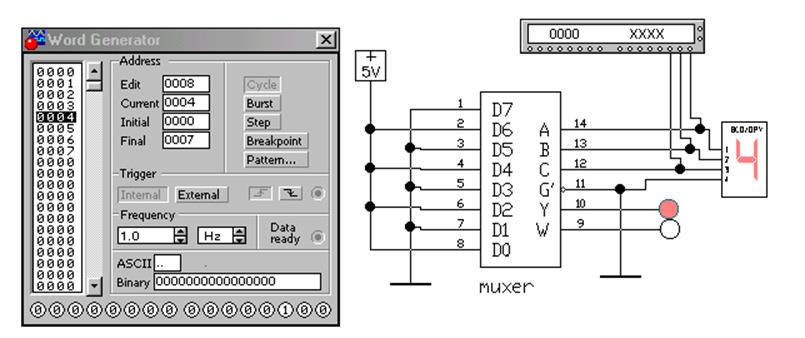

Слідуючий рисунок демонструє використання WordGenerator для визначен-ня логічної функції яка реалізується з допомогою досліджуємого мультиплек-сора. Генератор слів в режимі Pauseпослідовно формує адреси в двійковому форматі від 0000 до 0007, які відображаються на нижній горизонтальній строчці генератора і подаються на адресні входи мультиплексора . Логічні сигнали, що подані на біти шини даних послідовно будуть відображатись на виході Y в прямому коді, а на виході W- в зворотньому. Рисунок демонструє режим при якому адресний сигнал 0001 приєднує вхід D1 до виходу Y мультиплексора, внаслідок чого сигнал логічної 1 з його входу передається на вихід Y.

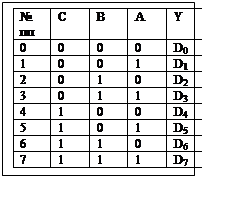

Таблиця станів мультиплексора одержана шляхом дослідження його роботи має вигляд

Логічна функція, що реалізується на попередньому рисунку з допомогою мультиплексора

Y = å 1, 3, 5, 7 = C’B’A +C’BA +CB’A + CBA.

Таблиця станів може бути отримана і шляхом використання логічного аналізатора. На рис. приводиться схема використання логічного аналізатора для визначення логічної функції, заданої на входах мультиплексора. В таблиці станів логічного аналізатора вона буде отримана після нажаття кнопки, яка вказує на перетворення принципової схеми в таблицю станів.

2. Порядок виконання роботи.

2.1. Вибрати з бази даних задані мікросхеми і вивексти їх на екран монітору.

2.2. Використовуючи Help визначитися з призначенням виводів мікросхеми. Якщо одержаної інформації недостатньо, то можна скористатись таблицями відповідності вітчизняних і зарубіжних мікросхем і довідковою літературою.

2.3. Скласти таблицю відповідності для входів і виходів мікросхеми.

2.4. По таблиці відповідності розробити алгоритм функціювання досліджуємої мікросхеми.

2.5. Скласти програму на одній з мов високого рівня для реалізації алгоритму функціювання досліджуємої мікросхеми.

2.6. Для досліджуємої схеми з фіксованими значеннями бітів вхідного слова відтворити часові діаграми роботи мультиплексора при зміні в часі адресних сигналів. Дати пояснення часовим діаграмам.

2.7. Розробити і реалізувати схему для циклічного перетворення двійкового коду, представленого на шині даних мультиплексора в паралельному форматі в послідовний формат з розділенням кожного вихідного слова двома одиничними (нульовими) тактами. Пояснити принцип роботи схеми і привести часові діаграми її роботи.

3. Підготовка звіту.

В звіті по виконаній роботі повинно бути:

- детальне описання виводів мікросхеми і пояснення її роботи;

- таблиця станів і алгоритм її функціювання;

- пояснення можливості використання для реалізації логічних функцій;

- програма реалізації алгоритму функціювання на одній з мов високого рівня;

- пояснення можливості використання мультиплексора для перетворення послідовного формату двійкового коду в паралельний.

4. Вимоги до атестації.

Для успішної атестації необхідно знати:

- алгоритми функціювання базових схем- мультиплексорів

- способи нарощування розрядності схем по шині даних;

- реалізовувати прості логічні функції на базі типових комбінаційних схем;

- принцип організації роботи мультиплексора для перетворення послідовного формату двійкового коду в паралельний;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.